Abstract

This paper reports two distinct architectures for digitally-controlled oscillators (DCOs) utilizing MOS varactor, designed in TSMC 180 nm CMOS technology. The first DCO design employs a CMOS inverter, while the second design features a Three-Transistors (3T) NAND gate as a delay stage inverter. Using these delay stages, three-bit, five-bit, and seven-bit controlled DCO circuits have been designed. For the inverter-based DCO circuit, the frequency spans from 4.844 to 2.708 GHz, 2.523 to 0.853 GHz, and 1.364 to 0.253 GHz, with a power consumption of 0.958 mW, 1.597 mW, and 2.236 mW for three-bit, five-bit, and seven-bit DCO variants, respectively. Further, the 3T-NAND gate-based DCO circuit exhibits oscillation frequencies ranging from 2.024 to 0.517 GHz, 0.867 to 0.131 GHz, and 0.341 to 0.033 GHz, with the resulting power consumption of 0.335 mW, 0.559 mW, and 0.782 mW. Equally significant, the proposed inverter-based DCO attains phase noise of − 102.61 dBc/Hz@1MHz, − 99.65 dBc/Hz@1MHz, and − 117.54 dBc/Hz@1MHz, accompanied by corresponding figures of merit (FoM) 174.94 dBc/Hz, 161.27 dBc/Hz, and 165.10 dBc/Hz for three-bit, five-bit, and seven-bit control words, respectively. For the 3T-NAND gate-based DCO, phase noise levels register at − 93.51 dBc/Hz@1MHz, − 113.07 dBc/Hz@1MHz, and − 106.96 dBc/Hz@1MHz, with FoM values of 160.23 dBc/Hz, 166.70 dBc/Hz, and 150.30 dBc/Hz for three-bit, five-bit, and seven-bit DCO variants, respectively. The comprehensive analysis of the proposed DCOs demonstrates the power supply variations, phase noise deviations, and frequency variations. The reported DCOs perform better with regard to output frequency range, power consumption, and overall FoM.

Article Highlights

-

The manuscript presents two new digitally controlled delay elements (DCDEs).

-

MOS varactor-based DCO circuits have been designed utilizing the proposed DCDEs.

-

Designs reported in the manuscript show lower power dissipation and an extensive frequency tuning range in comparison with traditional oscillator circuits.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Analog Phase Locked Loops (PLL) are a very attractive choice for contemporary radio frequency and wireless communication systems. The performance of analog PLLs largely depends on the voltage-controlled oscillator as it is considered the vital component and necessary building block of the PLL system [1,2,3]. However, analog PLLs contain analog components such as capacitors, resistors and filters that require a large chip area. In addition, it is hard to port analog PLLs from one fabrication process to another due to the sensitivity towards process parameters [4,5,6]. With the advancements in design technologies, the all-digital PLL (ADPLL) has become more popular due to its easy implementation across modern IC technologies and significantly smaller area requirements. ADPLLs employ all digital components, including the digitally-controlled oscillator (DCO). DCO is an essential element of this ADPLL structure, primarily controlling the frequency of oscillation [7, 8]. DCOs are more flexible and robust than their analog counterparts. Designing of ADPLLs requires monolithic DCOs with a wide frequency range and decent phase noise performance. The simplest form of DCO is an inverter-based ring type consisting of an odd count of delay stages/elements.

A digitally controlled delay element (DCDE) is the essential component of a DCO circuit. There are significant approaches for varying the delay of the DCDE. The first approach is the delay path selection in which multiplexors are utilized for the selection of the number of delay stages. This approach is not used standalone and is generally combined with additional techniques owing to its limited resolution [7,8,9,10,11,12]. The second method employs current-starved inverters as delay stages [9, 13, 14]. In this technique, binary-weighted PMOS/NMOS are used in the switching network that is controlled by the input vector [15, 16]. However, increased parasitic capacitance places a constraint on the maximum frequency of the DCO. The third approach is based on CMOS inverters with shunt MOS-based capacitors [14, 17, 18, 20]. In this, binary-weighted MOS-based capacitors are used to change the delay of the inverter by changing the capacitive load. However, shunt-type DCDE eventually becomes saturated as adding a greater number of switched capacitors results in reduced maximum frequency.

In the above-mentioned DCDE designs, there exists a basic trade-off between the tunning range and the maximum achievable frequency. More capacitive loading places a constraint on the maximum oscillation frequency that DCO can achieve and also leads to increased power dissipation. Hence, reducing the power dissipation of the DCO has become a major concern for its application in compact or Internet of Things (IoT) devices [4, 15].

In this manuscript, two new designs of DCDE have been reported. The DCDE designs are based on MOS varactors and an NMOS switching network. The remainder of the manuscript is structured as follows: Sect. 2 provides the design and working of the proposed DCO structures using the reported DCDEs. Further, Sect. 3 provides the results obtained for the proposed DCO circuits. Section 4 provides the conclusion of the reported work.

2 Proposed DCO circuit design

The DCO circuit is designed with two new proposed DCDEs as shown in Figs. 1 and 2. The relationship between the output oscillation frequency and the time delay of each stage can be expressed using the general Eq. (1):

where td is the delay offered by each stage and N is the number of delay stages. This equation highlights that the output frequency is inversely proportional to the delay offered by each stage. As the time delay of each stage decreases, the output frequency increases, and vice versa. This fundamental relationship underscores the dynamic interplay between time delay and output frequency within a DCO.

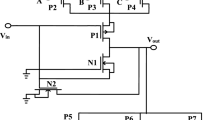

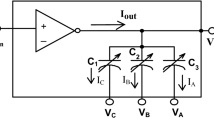

The first DCDE consists of a CMOS inverter and a digitally controlled load element implemented with three NMOS transistors (N2, N3, and N4) to provide the variable frequency. The second design has a 3T-NAND gate-based inverting stage, along with a digitally controlled load element connected at the output. The delay of an inverting stage is given by the Eq. (2):

where \({C}_{Load}\) is the output load capacitance, \({V}_{PP}\) is the peak-to-peak output voltage swing and \({I}_{D}\) is the cell current. Thus, the output oscillation frequency can be tuned by varying the capacitive load and by varying the cell current (\({I}_{D}\)) of the DCDE. Both the DCDEs employ the MOS varactor as the capacitive load at the output. NMOS transistors N2 and N3 work as two MOS varactors connected to the ground through a variable resistance designed with transistor N3. MOS varactor operates in a strong inversion mode when the gate voltage applied is greater than the threshold voltage i.e., VGS > VTH. In this inversion mode, the maximum MOS capacitance is given by the Eq. (3):

Consequently, by changing the width (W) of the MOS varactor, the capacitive load can be varied which in turn leads to a variable time delay offered by each stage and a tunable output frequency can be achieved. Also, the time delay td of the DCO is in turn a function of the input control word ‘D’ [9] and is given by the Eq. (4):

where D0 to Dn-1 are the control bits applied to the load element. Accordingly, by varying the control bits, current through the cell (\({{\varvec{I}}}_{{\varvec{D}}}\)) can be varied which leads to a large frequency range. Hence, the novel DCDE introduces an extra tuning method involving a variable capacitor, deviating from the conventional delay element that relies on an inverter configuration. This frequency adjustment technique, achieved without modifying the supply voltage, offers the benefit of reduced power dissipation. The equivalent circuit of the proposed DCDE is shown in Fig. 3.

For an NMOS-based varactor with the drain, source, and body connected together, the capacitance depends on the voltage applied at the gate and source terminal (VGS). Capacitance is higher with a negative VGS, and reduces with a positive VGS. With the application of digital bits D0, D1, and D2, the MOS varactors N6 and N7 provides a variable capacitance. When D0, D1, and D2 are set to [000], the VGS voltage for transistors N2 to N7 of the proposed DCO becomes positive and resulting in a reduction of MOS capacitance and subsequently an increase in the output frequency. The transistors N8 to N10 are binary weighted and contribute to capacitance value depending upon the digital bits D0, D1, and D2. Furthermore, applying a negative VGS to MOS varactors N2 to N7 leads to a reduction in the output frequency.

The power consumption of the DCO circuit is dependent on the supply voltage of the delay stage. Equation (5) gives the relationship between the dynamic component of power and the power supply (VDD) for the proposed DCO circuits.

where \(\alpha\) is the switching activity factor, \({C}_{Load}\) is the total load capacitance, \({f}_{clk}\) is the clock frequency, and VDD represents the power supply voltage. With increase in the supply voltage, the power consumption increases. Further, the proposed DCO circuits provide constant power with digital control variation as there is no change in the power supply voltage and demonstrate the advantage of low power over the traditional DCOs.

2.1 DCO circuit design I

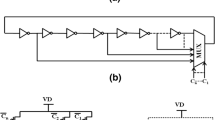

Proposed three-bit DCO circuit implemented with the first DCDE is shown in Fig. 4. The MOS transistor size used in the proposed DCO circuit is given in Table 1. The transistor length for all MOS transistors has been chosen as 0.18 µm. CMOS inverter is implemented with two MOS transistors P1 and N1. The MOS varactor has been designed with NMOS transistors N2 to N7. The switching network consists of binary-weighted NMOS transistors N8, N9, and N10 with 1.0, 2.0 and 4.0 µm MOS transistor width (W), respectively. By altering the control bits applied to the NMOS switching network, a tunable frequency is obtained. Further, Fig. 5 demonstrate the five-bit DCO design employing five DCDEs. Additionally, a seven-bit DCO has also been designed utilizing seven DCDEs.

2.2 DCO circuit design II

DCO circuit II is designed with a second proposed DCDE as shown in Fig. 6. In the alternative DCO design presented, the inverting stage adopts a 3T-NAND gate configuration [19], notable for its minimized transistor count when contrasted with the traditional method. Additionally, a direct connection between the power supply and ground is eliminated which leads to reduced leakage power and hence power consumption is less compared to DCO design I. A digitally controlled load element is connected at the output and consists of one NMOS switching network and two MOS varactors. Wide frequency range is achieved by modifying the control bits applied to the NMOS switching network. An optimized MOS transistor size utilized in the proposed 3T-NAND gate-based DCO is shown in Table 2. Furthermore, Fig. 7 shows the design of a five-bit DCO circuit with five DCDEs. In addition, a seven-bit DCO has been designed, employing seven DCDEs.

3 Results and discussions

The results of the presented DCO designs have been validated using mentor graphics in 180 nm CMOS technology. In the proposed DCDE, frequency tuning is achieved by varying the load element that is connected at the output terminal of each DCDE. Current flow through the load element varies depending upon the digital control bits applied to it. At the different combinations of control bits, the current varies which results in the variation of the delay time of the proposed DCDE. This, in turn, establishes a clear relationship between the output frequency of the ring oscillator and the delay time, resulting in a responsive frequency adjustment mechanism.

Table 3 demonstrates the outcomes of the three-bit DCO circuit. It is observed that by changing the input control bit from [000] to [111], the oscillation frequency decreases from 4.844 GHz to 2.708 GHz for inverter-based DCO design accompanied by a power consumption of 0.958 mW. Further, the output frequency varies from 2.024 GHz to 0.517 GHz for 3T-NAND gate-based DCO design with power dissipation of 0.335 mW. Results indicate lower power consumption in the DCO design with the second DCDE due to MOS transistor width optimization.

Tables 4 and 5 illustrate the frequency variations in five-bit and seven-bit DCO circuits, emphasizing the adaptability of the proposed designs. From the Table 4, it is evident that for five-bit DCO circuit, frequency ranges from 2.523 GHz to 0.853 GHz and 0.867 GHz to 0.131 GHz with the variation in control bit from [00000] to [11111]. The corresponding power consumption registers at 1.597 mW and 0.559 mW, respectively. Frequency tuning from 1.364 GHz to 0.253 GHz and from 0.341 GHz to 0.033GHz for a seven-bit DCO circuit designed with inverter-based DCDE and 3T-NAND gate-based DCDE is obtained with control bit variation from [0000000] to [1111111] as given in Table 5. The power consumption is measured at 2.236 mW, and 0.782 mW, respectively. Furthermore, the output oscillation frequency variations along with the control bit variations for three-bit, five-bit, and seven-bit DCOs is shown in Figs. 8, 9, and 10, offering a comprehensive visual understanding of the DCO behavior.

To further comprehend the robustness of our designs, the effects of variation in the power supply voltage on operating frequency and power consumption for inverter-based DCO circuits have been shown in Table 6. For different values of digital control bits, the output oscillation frequency exhibits a variation from 1.452 to 4.844 GHz with a variation in power supply voltage from 1.2 to 1.8 V. Power consumption variations ranging from 0.048 to 0.958 mW is obtained and recorded. The frequency and power variation curves are shown in Figs. 11 and 12. The frequency spectrum of the proposed DCO circuit with fundamental frequency at 4.8 GHz and its output waveform are shown in Fig. 13.

The performance of 3T-NAND gate-based DCO with variations in the supply voltage (VDD) from 1.2 to 1.8 V is presented in Table 7 for different values of digital control bits [D0–D2]. Figure 14 shows output frequency variations of 3T-NAND gate-based three-bit DCO with varying VDD. A frequency variation from 0.517 to 2.450 GHz is achieved as shown in Table 7 along with a minimal power dissipation of 0.184 to 0.336 mW, further highlights the flexibility inherent in our design. Figure 15 shows the power consumption variation curve at different values of the power supply (VDD). The results indicate that reducing the power supply voltage (VDD) leads to decreased power consumption in the proposed DCO circuit designs. The output frequency curve of the proposed DCO circuit with control bits [010] for a 3T-NAND gate-based three-bit DCO is shown in Fig. 16a. A complete frequency spectrum has been plotted with fundamental frequency at 1.25 GHz in Fig. 16b.

Further, the phase noise performance of the proposed DCO circuits has been studied and presented in Table 8. The proposed inverter-based DCO achieves phase noise of − 102.61 dBc/Hz, − 99.65 dBc/Hz, and − 117.54 dBc/Hz at 1 MHz for three-bit, five-bit, and seven-bit control words, respectively. In the case of the 3T-NAND gate-based DCO, the measured phase noise values are − 93.51 dBc/Hz, − 113.07 dBc/Hz, and − 106.96 dBc/Hz at 1 MHz for three-bit, five-bit, and seven-bit DCO variants, respectively. Phase noise waveform for the three-bit, five-bit, and seven-bit variants of the two DCO circuits is shown in Figs. 17 and 18.

The FoM (figure of merit) is another essential parameter for the evaluation of the performance of the DCO circuits and is calculated using the following equation [21]:

where \({\mathrm{f}}_{\mathrm{c}}\) is the carrier frequency, and \(\Delta \mathrm{f}\) is the offset from the carrier frequency, \({\mathrm{P}}_{\mathrm{DC}}\) denotes the DC power in mW and \(\mathrm{L }(\Delta \mathrm{f})\) represents the phase noise of the proposed DCO in dBc/Hz. FoM is the overall performance measure of a DCO. A higher figure of merit (FoM) is desirable for a DCO design as it indicates a wide frequency tuning range, lower power consumption and low phase noise. FoM varies from 174.94 to 150.30 dBc/Hz for the proposed DCO circuits. Compared with the reported circuits, the proposed DCOs demonstrate a better FoM. Table 8 summarizes the various performance parameters like phase noise, figure of merit (FoM) along with the digital tuning range, output frequency, and power consumption, all of which contribute to the overall assessment of the DCO's efficiency.

A comparison of the proposed DCO designs in terms of the output frequency range, power dissipation, phase noise, and FoM with the earlier published work has been summarized in Table 9. The incorporation of MOS varactors and novel DCDE designs distinguishes reported work from traditional methods, establishing it as a valuable contribution to the current state of research.

4 Conclusions

In this paper, two different DCO circuits in 180 nm technology, implementing digitally controlled MOS varactor loads to achieve wide frequency variation are presented. The first design utilizes a CMOS inverter as the inverting stage, with digitally controlled MOS varactors serving as capacitive loads in the DCDE. This inverter-based DCO covers a frequency range of 4.844 to 2.708 GHz, 2.523 to 0.853 GHz, and 1.364 to 0.253 GHz for three-bit, five-bit, and seven-bit configurations, respectively. The power consumption records at 0.958 mW, 1.597 mW, and 2.236 mW for these variants. Phase noise levels of − 102.61 dBc/Hz, − 99.65 dBc/Hz, and − 117.54 dBc/Hz at a 1 MHz offset are obtained. In the second DCO design, a 3T-NAND gate serves as the inverting stage, yielding frequency range of 2.024–0.517 GHz, 0.867–0.131 GHz, and 0.341–0.033 GHz for the corresponding three-bit, five-bit, and seven-bit control word. Phase noise measurements stand at − 93.51 dBc/Hz, − 113.07 dBc/Hz, and − 106.96 dBc/Hz at 1 MHz for three-bit, five-bit, and seven-bit control words, respectively. Power consumption of 0.335 mW, 0.559 mW, and 0.782 mW are obtained. Figures of merit (FoM) in the range of 174.94 to 150.30 dBc/Hz have been obtained. The proposed DCO designs show wide operating frequencies and decent phase noise along with improved FoM characteristics making them suitable for high-frequency applications. However, limitations in the specific CMOS technology and trade-offs between frequency and power persist. Future research could explore advanced CMOS technologies, tackle frequency-power trade-offs, and investigate adaptive tuning mechanisms to enhance robustness. These advancements hold the potential to create more efficient and versatile DCOs for diverse applications in communication and sensing systems.

Data availability

All data generated or analyzed during this study are included in this published article.

References

Catli B and Hella MM (2008) A 0.5-V 3.6/5.2 GHz CMOS multi-band LC VCO for ultra low-voltage wireless applications. In: 2008 IEEE International Symposium on Circuits and Systems, Seattle, pp. 996-999. https://doi.org/10.1109/ISCAS.2008.4541588

Chen YJ, du Plessis M (2006) An integrated 0.35 μm CMOS optical receiver with clock and data recovery circuit. Microelectron J 37(9):985–992. https://doi.org/10.1016/j.mejo.2006.01.003

de Paula LS, Bampi S, Fabris E and Susin A A (2008) A wide band CMOS differential voltage-controlled ring oscillator. In: 2008 Joint 6th International IEEE Northeast Workshop on Circuits and Systems and TAISA Conference, Montreal, Canada, pp. 9-12. https://doi.org/10.1109/NEWCAS.2008.4606308

Olsson T, Nilsson P (2004) A digitally controlled PLL for SoC applications. IEEE J Solid-State Circuits 39(5):751–760. https://doi.org/10.1109/JSSC.2004.826333

Kumar M, Arya SK, Pandey S (2011) Digitally controlled oscillator design with a variable capacitance XOR gate. J Semicond 32(10):105001. https://doi.org/10.1088/1674-4926/32/10/105001

Elrabaa MES (2013) A portable high-frequency digitally controlled oscillator (DCO). Integration VLSI J 47:339–346. https://doi.org/10.1016/j.vlsi.2013.10.009

Chiang J-S, Chen K-Y (1999) The design of an all-digital phase-locked loop with small DCO hardware and fast phase lock. IEEE Trans Circuits Syst 46(7):945–950. https://doi.org/10.1109/82.775392

Wu CT, Wang W, Wey IC, Wu AY (2005) A scalable DCO design for portable ADPLL designs. In: 2005 IEEE International Symposium on Circuits and Systems, pp. 5449–5452 Vol. 6. https://doi.org/10.1109/ISCAS.2005.1465869

Zhao J, Kim YB (2010) A Low-power digitally controlled oscillator for all digital phase-locked loops. VLSI Design. https://doi.org/10.1155/2010/946710

Sheng D, Chung CC, Lee CY (2006) An all-digital phase-locked loop with high-resolution for SoC applications. In: Proceedings of the International Symposium on VLSI Design, Automation and Test, pp.1–4. https://doi.org/10.1109/VDAT.2006.258161

D. Sheng, C. Chung and C. Lee. An ultra-low-power and portable digitally controlled oscillator for SoC Applications. In: IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 54, no. 11, pp. 954–958. https://doi.org/10.1109/TCSII.2007.903782

Hsu S, Yu J, Lee C (2010) A sub-10-μW digitally controlled oscillator based on hysteresis delay cell topologies for WBAN applications. IEEE Trans Circuits Syst II 57(12):951–955. https://doi.org/10.1109/TCSII.2010.2087991

Staszewski RB, Balsara PT (2004) Phase-domain all-digital phase-locked loop. IEEE Trans Circuits Syst II 52(3):159–163. https://doi.org/10.1109/TCSII.2004.842067

Raha P, Randall S, Jennings R, Helmick B, Amerasekera A, Haroun B (2002) A robust digital delay line architecture in a 0.13/spl mu/m CMOS technology node for reduced design and process sensitivities. In: Proceedings International Symposium on Quality Electronic Design, San Jose, pp. 148–153. https://doi.org/10.1109/ISQED.2002.996719

Sheng D, Chen W-Y, Huang H-T, Tai L (2021) Digitally controlled oscillator with high timing resolution and low complexity for clock generation. Sensors 21:1377. https://doi.org/10.3390/s21041377

Maymandi-Nejad M, Sachdev M (2005) A monotonic digitally controlled delay element. IEEE J Solid-State Circuits 40(11):2212–2219. https://doi.org/10.1109/JSSC.2005.857370

Tomar A, Pokharel RK, Nizhnik O, Kanaya H, Yoshida K (2007) Design of 1.1 GHz highly linear digitally-controlled ring oscillator with wide tuning range. In: IEEE International Workshop on Radio-Frequency Integration Technology, Singapore, pp. 82–85. https://doi.org/10.1109/RFIT.2007.4443926

Dwivedi D, Kumar M (2009) Design of a 3-bit digital control oscillator (DCO) using IMOS varactor tuning. Analog Integrated Circuits Signal Proc 100(3):613–620. https://doi.org/10.1007/s10470-019-01506-x4

Kumar M (2013) A low power voltage controlled oscillator design. ISRN Electron. https://doi.org/10.1155/2013/987179

Kumar M (2023) Design of low-power CMOS VCO with three transistors NAND gate and MOS varactor. J Inst Eng India Ser B 104:851–858. https://doi.org/10.1007/s40031-023-00898-9

Razavi B, Microelectronics RF (1998) Upper saddle river. Prentice Hall, Hoboken

Staszewski RB, Hung C-M, Leipold D, Balsara PT (2003) A first multigigahertz digitally controlled oscillator for wireless applications. IEEE Trans Microwave Theory Techn 51(11):2154–2164. https://doi.org/10.1109/TMTT.2003.818579

Li C, Liscidini A (2016) Class-C PA-VCO cell for FSK and GFSK transmitters. IEEE J Solid-State Circuits 51(7):1537–1546. https://doi.org/10.1109/JSSC.2016.2554148

Saint-Laurent M. and Muyshondt GP (2001) A digitally controlled oscillator constructed using adjustable resistors. 2001 Southwest Symposium on Mixed-Signal Design (Cat. No.01EX475), Austin, pp. 80-82. https://doi.org/10.1109/SSMSD.2001.914942

Pokharel RK, Tomar A, Kanaya H and Yoshida K (2008) Design of highly linear, 1GHz 8-bit digitally controlled ring oscillator with wide tuning range in 0.18um CMOS process. In: 2008 China-Japan Joint Microwave Conference, Shanghai, pp. 623-626. https://doi.org/10.1109/CJMW.2008.4772508

Kumar N, Kumar M (2019) Low power, ring VCO with pre-charge and pre-discharge circuit for 4 GHz–6.1 GHz applications in 0.18 μm CMOS. J Circuits Syst Comput 28:1950182. https://doi.org/10.1142/S0218126619501822

Dwivedi D, Kumar M, Niranjan V (2021) Design of power-efficient CMOS based oscillator circuit with varactor tuning control. SN Appl Sci 3:487. https://doi.org/10.1007/s42452-021-04501-y

Funding

The authors declare that no funds, grants, or other support were received during the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

All authors contributed to the conceptualization. Design, data curation, analysis and validation were performed by SD. Supervision and writing review was done by MK. All authors have read and approved the final manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors have no relevant financial or non-financial interests to disclose.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Dabas, S., Kumar, M. A low power varactor based digitally controlled oscillator design in 180 nm CMOS technology. SN Appl. Sci. 5, 295 (2023). https://doi.org/10.1007/s42452-023-05519-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-023-05519-0