Abstract

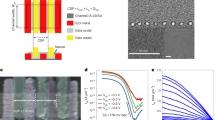

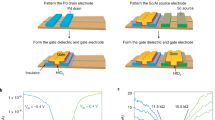

Thanks to its single-atomic-layer structure, high carrier transport, and low power dissipation, carbon nanotube electronics is a leading candidate towards beyond-silicon technologies. Its low temperature fabrication processes enable three-dimensional (3D) integration with logic and memory (static random access memory (SRAM), magnetic random access memory (MRAM), resistive random access memory (RRAM), etc.) to realize efficient near-memory computing. Importantly, carbon nanotube transistors require good thermal stability up to 400 °C processing temperature to be compatible with back-end-of-line (BEOL) process, which has not been previously addressed. In this work, we developed a robust wafer-scale process to build complementary carbon nanotube transistors with high thermal stability and good uniformity, where AIN was employed as electrostatic do** layer. The gate stack and passivation layer were optimized to realize high-quality interfaces. Specifically, we demonstrate 1-bit carbon nanotube full adders working under 250 °C with rail-to-rail outputs.

Similar content being viewed by others

References

**e, Y. N.; Zhong, D. L.; Fan, C. W.; Deng, X. S.; Peng, L. M.; Zhang, Z. Y. Highly temperature-stable carbon nanotube transistors and gigahertz integrated circuits for cryogenic electronics. Adv. Electr. Mater. 2021, 7, 2100202.

Bishop, M. D.; Hills, G.; Srimani, T.; Lau, C.; Murphy, D.; Fuller, S.; Humes, J.; Ratkovich, A.; Nelson, M.; Shulaker, M. M. Fabrication of carbon nanotube field-effect transistors in commercial silicon manufacturing facilities. Nat. Electron. 2020, 3, 492–501.

Lau, C.; Srimani, T.; Bishop, M. D.; Hills, G.; Shulaker, M. M. Tunable n-type do** of carbon nanotubes through engineered atomic layer deposition HfOx films. ACS Nano 0018, 12, 10924–10931.

Shi, H. W.; Ding, L.; Zhong, D. L.; Han, J.; Liu, L. J.; Xu, L.; Sun, P. K.; Wang, H.; Zhou, J. S.; Fang, L. et al. Radiofrequency transistors based on aligned carbon nanotube arrays. Nat. Electron. 2021, 4, 405–415.

Pei, T.; Zhang, Z. Y.; Wang, Z. X.; Ding, L.; Wang, S.; Peng, L. M. Temperature performance of do**-free top-gate CNT field-effect transistors: Potential for low- and high-temperature electronics. Adv. Funct. Mater. 2011, 21, 1843–1849.

Cao, Q. Carbon nanotube transistor technology for more-Moore scaling. Nano Res. 2021, 14, 3051–3069.

Cao, Q.; Tersoff, J.; Farmer, D. B.; Zhu, Y.; Han, S. J. Carbon nanotube transistors scaled to a 40-nanometer footprint. Science 2017, 356, 1369–1372.

Liu, L. J.; Han, J.; Xu, L.; Zhou, J. S.; Zhao, C. Y.; Ding, S. J.; Shi, H. W.; **ao, M. M.; Ding, L.; Ma, Z. et al. Aligned, high-density semiconducting carbon nanotube arrays for high-performance electronics. Science 2020, 368, 850–856.

Hills, G.; Lau, C.; Wright, A.; Fuller, S.; Bishop, M. D.; Srimani, T.; Kanhaiya, P.; Ho, R.; Amer, A.; Stein, Y. et al. Modern microprocessor built from complementary carbon nanotube transistors. Nature 2019, 572, 595–602.

Batude, P.; Brunet, L.; Fenouillet-Beranger, C.; Andrieu, F.; Colinge, J. P.; Lattard, D.; Vianello, E.; Thuries, S.; Billoint, O.; Vivet, P. et al. 3D sequential integration: Application-driven technological achievements and guidelines. In 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2017, pp 3.1.1–3.1.4.

Aly, M. M. S.; Gao, M. Y.; Hills, G.; Lee, C. S.; Pitner, G.; Shulaker, M. M.; Wu, T. F.; Asheghi, M.; Bokor, J.; Franchetti, F. et al. Energy-efficient abundant-data computing: The N3XT 1,000x. Computer 2015, 48, 24–33.

Singh, G.; Chelini, L.; Corda, S.; Awan, A. J.; Stuijk, S.; Jordans, R.; Corporaal, H.; Boonstra, A. J. Near-memory computing: Past, present, and future. Microprocess. Microsyst. 2019, 71, 102868.

Shulaker, M. M.; Hills, G.; Park, R. S.; Howe, R. T.; Saraswat, K.; Wong, H. S. P.; Mitra, S. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. Nature 2017, 547, 74–78.

**e, Y. N.; Zhang, Z. Y.; Zhong, D. L.; Peng, L. M. Speeding up carbon nanotube integrated circuits through three-dimensional architecture. Nano Res. 2019, 12, 1810–1816.

Peng, L. M.; Zhang, Z. Y.; Qiu, C. G. Carbon nanotube digital electronics. Nat. Electron. 2019, 2, 499–505.

Yang, Y. J.; Ding, L.; Han, J.; Zhang, Z. Y.; Peng, L. M. High-performance complementary transistors and medium-scale integrated circuits based on carbon nanotube thin films. ACS Nano 2017, 11, 4124–4132.

Tang, J. S.; Cao, Q.; Tulevski, G.; Jenkins, K. A.; Nela, L.; Farmer, D. B.; Han, S. J. Flexible CMOS integrated circuits based on carbon nanotubes with sub-10 ns stage delays. Nat. Electron. 2018, 1, 191–196.

Srimani, T.; Hills, G.; Bishop, M.; Lau, C.; Kanhaiya, P.; Ho, R.; Amer, A.; Chao, M.; Yu, A.; Wright, A. et al. Heterogeneous integration of BEOL logic and memory in a commercial foundry: Multi-tier complementary carbon nanotube logic and resistive RAM at a 130 nm node. In 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 2020, pp 1–2.

Swerts, J.; Liu, E.; Couet, S.; Mertens, S.; Rao, S.; Kim, W.; Garello, K.; Souriau, L.; Kundu, S.; Crotti, D. et al. Solving the BEOL compatibility challenge of top-pinned magnetic tunnel junction stacks. In 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2017, pp 38.6. 1–38.6. 4.

Jan, G.; Thomas, L.; Le, S.; Lee, Y. J.; Liu, H. L.; Zhu, J.; Tong, R. Y.; Pi, K. Y.; Wang, Y. J.; Shen, D. N. et al. Demonstration of fully functional 8 Mb perpendicular STT-MRAM chips with sub-5 ns writing for non-volatile embedded memories. In 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 2014, pp 1–2.

Yu, S. M.; Chen, P. Y. Emerging memory technologies: Recent trends and prospects. IEEE Solid-State Circuits Mag. 2016, 8, 43–56.

Cheng, H. Y.; Raoux, S.; Chen, Y. C. The impact of film thickness and melt-quenched phase on the phase transition characteristics of Ge2Sb2Te5. J. Appl. Phys. 2010, 107, 074308.

Biggs, J.; Myers, J.; Kufel, J.; Ozer, E.; Craske, S.; Sou, A.; Ramsdale, C.; Williamson, K.; Price, R.; White, S. A natively flexible 32-bit arm microprocessor. Nature 2021, 595, 532–536.

Acknowledgements

The authors gratefully acknowledge fundings from the National Natural Science Foundation of China (No. 61888102) and the Bei**g Municipal Science and Technology Commission (No. D171100006617002).

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

About this article

Cite this article

Wei, N., Gao, N., Xu, H. et al. Wafer-scale fabrication of carbon-nanotube-based CMOS transistors and circuits with high thermal stability. Nano Res. 15, 9875–9880 (2022). https://doi.org/10.1007/s12274-022-4259-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12274-022-4259-9