Abstract

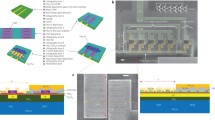

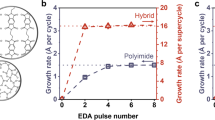

Semiconducting carbon nanotube (CNT) field effect transistor (FET) is attractive for constructing three-dimensional (3D) integrated circuits (ICs) because of its low-temperature processes and low power dissipation. However, CNT based 3D ICs reported usually suffered from lower performance than that of monolayer CNT ICs. In this work, we develop a 3D IC technology through integrating multi-layer high performance CNT film FETs into one chip, and show that it promotes the operation speed of CNT based 3D ICs considerably. We also explore the advantage on ICs of 3D architecture, which brings 38% improvement on speed over two-dimensional (2D) one. Specially, we demonstrate the fabrication of 3D five-stage ring-oscillator circuits with an oscillation frequency of up to 680 MHz and stage delay of 0.15 ns, which represents the highest speed of 3D CNT-based ICs.

Similar content being viewed by others

References

Dennard, R. H.; Gaensslen, F. H.; Yu, H. N.; Rideout, V. L.; Bassous, E.; Leblanc, A. R. Design of ion-implanted MOSFET’s with very small physical dimensions. Proc. IEEE 1999, 87, 668–678.

Davis, J. A.; Venkatesan, R.; Kaloyeros, A.; Beylansky, M.; Souri, S. J.; Banerjee, K.; Saraswat, K. C.; Rahman, A.; Reif, R.; Meindl, J. D. Interconnect limits on gigascale integration (GSI) in the 21st century. Proc. IEEE 2001, 89, 305–324.

Frank, D. J.; Dennard, R. H.; Nowak, E.; Solomon, P. M.; Taur, Y.; Wong, H. S. P. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 2001, 89, 259–288.

Skotnicki, T.; Fenouillet-Beranger, C.; Gallon, C.; Boeuf, F.; Monfray, S.; Payet, F.; Pouydebasque, A.; Szczap, M.; Farcy, A.; Arnaud, F. et al. Innovative materials, devices, and CMOS technologies for low-power mobile multimedia. IEEE Trans. Electron Devices 2008, 55, 96–130.

Lieber, C. M. Nanoscale science and technology: Building a big future from small things. MRS Bull. 2003, 28, 486–491.

Thelander, C.; Agarwal, P.; Brongersma, S.; Eymery, J.; Feiner, L. F.; Forchel, A.; Scheffler, M.; Riess, W.; Ohlsson, B.; Gösele, U. et al. Nanowire-based one-dimensional electronics. Materialstoday 2006, 9, 28–35.

McEuen, P. L.; Fuhrer, M. S.; Park, H. Single-walled carbon nanotube electronics. IEEE Trans. Nanotechnol. 2002, 1, 78–85.

Javey, A.; Guo, J.; Wang, Q.; Lundstrom, M.; Dai, H. J. Ballistic carbon nanotube field-effect transistors. Nature 2003, 424, 654–657.

Topol, A. W.; La Tulipe, D. C.; Shi, L.; Frank, D. J.; Bernstein, K.; Steen, S. E.; Kumar, A.; Singco, G. U.; Young, A. M.; Guarini, K. W. et al. Three-dimensional integrated circuits. IBM J. Res. Dev. 2006, 50, 491–506.

Das, S.; Chandrakasan, A.; Reif, R. Three-dimensional integrated circuits: Performance, design methodology, and CAD tools. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI, 2003, Tampa, FL, USA, 2003, pp 13–18.

England, L.; Arsovski, I. Advanced packaging saves the day!—How TSV technology will enable continued scaling. In Proceedings of 2017 IEEE International Electron Devices Meeting, San Francisco, CA, 2017, pp 3.5.1-3.5.4.

Kim, K. M.; Sinha, S.; Cline, B.; Yeric, G.; Lim, S. K. Four-tier monolithic 3D ICs: Tier partitioning methodology and power benefit study. In Proceedings of the 2016 International Symposium on Low Power Electronics and Design. San Francisco Airport, CA, USA, 2016, pp 70–75.

Lin, M. J.; El Gamal, A.; Lu, Y. C.; Wong, S. Performance benefits of monolithically stacked 3-D FPGA. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2007, 26, 216–229.

Sabry Aly, M. M.; Gao, M. Y.; Hills, G.; Lee, C. S.; Pitner, G.; Shulaker, M. M.; Wu, T. F.; Asheghi, M.; Bokor, J.; Franchetti, F. et al. Energy-efficient abundant-data computing: The N3XT 1,000x. Computer 2015, 48, 24–33.

Wu, T. T.; Shen, C. H.; Shieh, J. M.; Huang, W. H.; Wang, H. H.; Hsueh, F. K.; Chen, H. C.; Yang, C. C.; Hsieh, T. Y.; Chen, B. Y. et al. Low-cost and TSV-free monolithic 3D-IC with heterogeneous integration of logic, memory and sensor analogy circuitry for Internet of Things. In Proceedings of 2015 IEEE International Electron Devices Meeting, Washington, DC, USA, 2015, pp 25.4.1-25.4.4.

Hsueh, F. K.; Shen, C. H.; Shieh, J. M.; Li, K. S.; Chen, H. C.; Huang, W. H.; Wang, H. H.; Yang, C. C.; Hsieh, T. Y.; Lin, C. H. et al. First fully functionalized monolithic 3D+ IoT chip with 0.5 V light-electricity power management, 6.8 GHz wireless-communication VCO, and 4-layer vertical ReRAM. In Proceedings of 2016 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 2016, pp 2.3.1-2.3.4.

Fenouillet-Beranger, C.; Beaurepaire, S.; Deprat, F.; de Sousa, A. A.; Brunet, L.; Batude, P.; Rozeau, O.; Andrieu, F.; Besombes, P.; Samson, M. P. et al. Guidelines for intermediate back end of line (BEOL) for 3D sequential integration. 2017 47th European Solid-State Device Research Conference, Leuven, Belgium, 2017, pp 252–255.

Vinet, M.; Batude, P.; Tabone, C.; Previtali, B.; LeRoyer, C.; Pouydebasque, A.; Clavelier, L.; Valentian, A.; Thomas, O.; Michaud, S. et al. 3D monolithic integration: Technological challenges and electrical results. Microelectron. Eng. 2011, 88, 331–335.

Qiu, C. G.; Zhang, Z. Y.; **ao, M. M.; Yang, Y. J.; Zhong, D. L.; Peng, L. M. Scaling carbon nanotube complementary transistors to 5-nm gate lengths. Science 2017, 355, 271–276.

Cavin, R. K.; Lugli, P.; Zhirnov, V. V. Science and engineering beyond Moore’s law. Proc. IEEE 2012, 100, 1720–1749.

Guo, J.; Hasan, S.; Javey, A.; Bosman, G.; Lundstrom, M. S. Assessment of high-frequency performance potential of carbon nanotube transistors. IEEE Trans. Nanotechnol. 2005, 4, 715–721.

Tulevski, G. S.; Franklin, A. D.; Frank, D.; Lobez, J. M.; Cao, Q.; Park, H.; Afzali, A.; Han, S. J.; Hannon, J. B.; Haensch, W. Toward high-performance digital logic technology with carbon nanotubes. ACS Nano 2014, 8, 8730–8745.

Cao, Q.; Tersoff, J.; Farmer, D. B.; Zhu, Y.; Han, S. J. Carbon nanotube transistors scaled to a 40-nanometer footprint. Science 2017, 356, 1369–1372.

Franklin, A. D.; Luisier, M.; Han, S. J.; Tulevski, G.; Breslin, C. M.; Gignac, L.; Lundstrom, M. S.; Haensch, W. Sub-10 nm carbon nanotube transistor. Nano Lett. 2012, 12, 758–762.

Shulaker, M. M.; Hills, G.; Park, R. S.; Howe, R. T.; Saraswat, K.; Wong, H. S. P.; Mitra, S. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. Nature 2017, 547, 74–78.

Wei, H.; Patil, N.; Lin, A.; Wong, H. S. P.; Mitra, S. Monolithic three-dimensional integrated circuits using carbon nanotube FETs and interconnects. In Proceedings of 2009 IEEE International Electron Devices Meeting, Baltimore, MD, USA, 2009, pp 1–4.

Wei, H.; Shulaker, M.; Wong, H. S. P.; Mitra, S. Monolithic three-dimensional integration of carbon nanotube FET complementary logic circuits. In Proceedings of 2013 IEEE International Electron Devices Meeting, IEEE, 2013, pp 19.7.1-19.7.4.

Chen, B. Y.; Zhang, P. P.; Ding, L.; Han, J.; Qiu, S.; Li, Q. W.; Zhang, Z. Y.; Peng, L. M. Highly uniform carbon nanotube field-effect transistors and medium scale integrated circuits. Nano Lett. 2016, 16, 5120–5128.

Zhong, D. L.; **ao, M. M.; Zhang, Z. Y.; Peng, L. M. Solution-processed carbon nanotubes based transistors with current density of 1.7 mA/μm and peak transconductance of 0.8 mS/μm. 2017 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 2017, pp 5.6.1-5.6.4.

Yang, Y. J.; Ding, L.; Han, J.; Zhang, Z. Y.; Peng, L. M. High-performance complementary transistors and medium-scale integrated circuits based on carbon nanotube thin films. ACS Nano 2017, 11, 4124–4132.

**ao, M. M.; Liang, S. B.; Han, J.; Zhong, D. L.; Liu, J. X.; Zhang, Z. Y.; Peng, L. M. Batch fabrication of ultrasensitive carbon nanotube hydrogen sensors with sub-ppm detection limit. ACS Sens. 2018, 3, 749–756.

Geier, M. L.; McMorrow, J. J.; Xu, W. C.; Zhu, J.; Kim, C. H.; Marks, T. J.; Hersam, M. C. Solution-processed carbon nanotube thin-film complementary static random access memory. Nat. Nanotechnol. 2015, 10, 944–948.

Ding, L.; Liang, S. B.; Pei, T.; Zhang, Z. Y.; Wang, S.; Zhou, W. W.; Liu, J.; Peng, L. M. Carbon nanotube based ultra-low voltage integrated circuits: Scaling down to 0.4 V. Appl. Phys. Lett. 2012, 100, 263116.

Banerjee, K.; Souri, S. J.; Kapur, P.; Saraswat, K. C. 3-D ICs: A novel chip design for improving deep-submicrometer interconnect performance and systems-on-chip integration. Proc. IEEE 2001, 89, 602–633.

Zhao, Y. D.; Li, Q. Q.; **ao, X. Y.; Li, G. H.; **, Y. H.; Jiang, K. L.; Wang, J. P.; Fan, S. S. Three-dimensional flexible complementary metal- oxide-semiconductor logic circuits based on two-layer stacks of single-walled carbon nanotube networks. ACS Nano 2016, 10, 2193–2202.

Zhang, P. P.; Qiu, C. G.; Zhang, Z. Y.; Ding, L.; Chen, B. Y.; Peng, L. M. Performance projections for ballistic carbon nanotube FinFET at circuit level. Nano Res. 2016, 9, 1785–1794.

Wang, C.; Zhang, J. L.; Ryu, K.; Badmaev, A.; de Arco, L. G.; Zhou, C. W. Wafer-scale fabrication of separated carbon nanotube thin-film transistors for display applications. Nano Lett. 2009, 9, 4285–4291.

Zhao, C. Y.; Zhong, D. L.; Qiu, C. G.; Han, J.; Zhang, Z. Y.; Peng, L. M. Improving subthreshold swing to thermionic emission limit in carbon nanotube network film-based field-effect. Appl. Phys. Lett. 2018, 112, 053102.

Kaufman, F. B.; Thompson, D. B.; Broadie, R. E.; Jaso, M. A.; Guthrie, W. L.; Pearson, D. J.; Small, M. B. Chemical-mechanical polishing for fabricating patterned W metal features as chip interconnects. J. Electrochem. Soc. 1991, 138, 3460–3465.

Ahn, J. H.; Kim, H. S.; Lee, K. J.; Jeon, S.; Kang, S. J.; Sun, Y. G.; Nuzzo, R. G.; Rogers, J. A. Heterogeneous three-dimensional electronics by use of printed semiconductor nanomaterials. Science 2006, 314, 1754–1757.

Nam, S. W.; Jiang, X. C.; **ong, Q. H.; Ham, D.; Lieber, C. M. Vertically integrated, three-dimensional nanowire complementary metal-oxide-semiconductor circuits. Proc. Natl. Acad. Sci. USA 2009, 106, 21035–21038.

Zhong, D. L.; Zhang, Z. Y.; Ding, L.; Han, J.; **ao, M. M.; Si, J.; Xu, L.; Qiu, C. G.; Peng, L. M. Gigahertz integrated circuits based on carbon nanotube films. Nat. Electron. 2018, 1, 40–45.

Han, S. J.; Tang, J. S.; Kumar, B.; Falk, A.; Farmer, D.; Tulevski, G.; Jenkins, K.; Afzali, A.; Oida, S.; Ott, J. et al. High-speed logic integrated circuits with solution-processed self-assembled carbon nanotubes. Nat. Nanotechnol., 2017, 12, 861–865.

Acknowledgements

This work was supported by the National Key Research & Development Program (No. 2016YFA0201901), the National Natural Science Foundation of China (Nos. 61621061, 61427901 and 61888102) and the Bei**g Municipal Science and Technology Commission (No. D171100006617002 1-2).

Author information

Authors and Affiliations

Corresponding authors

Electronic Supplementary Material

Rights and permissions

About this article

Cite this article

**e, Y., Zhang, Z., Zhong, D. et al. Speeding up carbon nanotube integrated circuits through three-dimensional architecture. Nano Res. 12, 1810–1816 (2019). https://doi.org/10.1007/s12274-019-2436-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12274-019-2436-2