Abstract

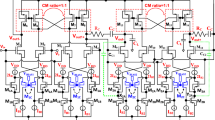

An efficient architecture of a high-performance ultra-low-voltage gate-driven two-stage pseudo-fully differential operational transconductance amplifier (OTA) is presented. The proposed subthreshold-region operated OTA utilizes two identical conventional current-mirror-based source coupled pseudo-differential amplifiers with their cross-connected gate as core amplifier blocks. The input core differential pair exploiting forward body terminal biasing scheme at output load employed in cascaded stages essentially improves the overall transconductance more than twice compared to the conventional pseudo-differential pair based OTA and achieves near rail-to-rail output voltage swing (90.2% of supply voltage) for near rail-to-rail input common-mode voltage (94.92% of supply voltage). The circuit is designed and optimized using gm/ID technique associated with the Particle Swarm Optimization (PSO) algorithm with a single supply of 0.35 V for a capacitive load of 10 pF and simulated in Cadence Virtuoso analog environment using UMC 180-nm CMOS technology. Post-layout simulations have been accomplished to justify the performance of the proposed OTA. It achieves an open-loop gain of 83.00 dB, phase margin of 61.48°, and power dissipation of 35.04 nW at a unity gain frequency of 24.78 kHz. A low-frequency continuous second-order Gm-C filter is also implemented to validate its workability. Simulation results of this work are compared to the state-of-the-art architecture available, and enhanced performance is validated.

Similar content being viewed by others

Data availability

The authors confirm that all data are included within the manuscript.

References

Calhoun, B. H., Daly, D. C., Verma, N., Finchelstein, D. F., Wentzloff, D. D., Wang, A., Cho, S. H., & Chandrakasan, A. P. (2005). Design considerations for ultra-low energy wireless microsensor nodes. IEEE Transactions on Computers, 54(6), 727–740.

Tabesh, A., & Fréchette, L. G. (2009). A low-power stand-alone adaptive circuit for harvesting energy from a piezoelectric micropower generator. IEEE Transactions on Industrial Electronics, 57(3), 840–849.

Romani, A., Filippi, M., & Tartagni, M. (2013). Micropower design of a fully autonomous energy harvesting circuit for arrays of piezoelectric transducers. IEEE Transactions on Power Electronics, 29(2), 729–739.

Harrison, R. R., & Charles, C. (2003). A low-power low-noise CMOS amplifier for neural recording applications. IEEE Journal of solid-state circuits, 38(6), 958–965.

Chandrakasan, A. P., Verma, N., & Daly, D. C. (2008). Ultralow-power electronics for biomedical applications. Annual Review of Biomedical Engineering, 10, 247–274.

Suda, N., Nishanth, P. V., Basak, D., Sharma, D., & Paily, R. P. (2014). A 0.5-V low power analog front-end for heart-rate detector. Analog Integrated Circuits and Signal Processing, 81(2), 417–430.

Li, Y., Poon, C. C., & Zhang, Y. T. (2010). Analog integrated circuits design for processing physiological signals. IEEE Reviews in Biomedical Engineering, 3, 93–105.

Rajput, S. S., & Jamuar, S. S. (2002). Low voltage analog circuit design techniques. IEEE Circuits and Systems Magazine, 2(1), 24–42.

Rajput, S. S., & Jamuar, S. S. (2001). Low voltage, low power, high performance current mirror for portable analogue and mixed mode applications. IEE Proceedings-Circuits, Devices and Systems, 148(5), 273–278.

Chatterjee, S., Tsividis, Y., & Kinget, P. (2005). 0.5-V analog circuit techniques and their application in OTA and filter design. IEEE Journal of Solid-State Circuits, 40(12), 2373–2387.

Kulej, T., & Khateb, F. (2019). A compact 0.3-V class AB bulk-driven OTA. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 28(1), 224–232. https://doi.org/10.1109/TVLSI.2019.2937206

Abdelfattah, O., Roberts, G. W., Shih, I., & Shih, Y. C. (2015). An ultra-low-voltage CMOS process-insensitive self-biased OTA with rail-to-rail input range. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(10), 2380–2390.

Kulej, T., & Khateb, F. (2018). Design and implementation of sub 0.5-V OTAs in 0.18-μm CMOS. International Journal of Circuit Theory and Applications, 46(6), 1129–1143.

Cabrera-Bernal, E., Pennisi, S., Grasso, A. D., Torralba, A., & Carvajal, R. G. (2016). 0.7-V three-stage class-AB CMOS operational transconductance amplifier. IEEE Transactions on Circuits and Systems I: Regular Papers, 63(11), 1807–1815.

Grasso, A. D., Pennisi, S., Scotti, G., & Trifiletti, A. (2017). 0.9-V class-AB Miller OTA in 035-μm CMOS with threshold-lowered non-tailed differential pair. IEEE Transactions on Circuits and Systems I: Regular Papers, 64(7), 1740–1747.

Sharan, T., & Bhadauria, V. (2017). Fully differential, bulk driven, class AB, sub-threshold OTA with enhanced slew rates and gain. Journal of Circuits, Systems, and Computers, 26(1), 1750001.

Ferreira, L. H., Pimenta, T. C., & Moreno, R. L. (2007). An ultra-low-voltage ultra-low-power CMOS miller OTA with rail-to-rail input/output swing. IEEE Transactions on Circuits and Systems II: Express Briefs, 54(10), 843–847.

Blalock, B. J., Allen, P. E., & Rincon-Mora, G. A. (1998). Designing 1-V op amps using standard digital CMOS technology. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 45(7), 769–780.

Stockstad, T., & Yoshizawa, H. (2002). A 0.9-V 0.5-µA rail-to-rail CMOS operational amplifier. IEEE Journal of Solid-State Circuits, 37(3), 286–292.

Lehmann, T., & Cassia, M. (2001). 1-V power supply CMOS cascode amplifier. IEEE Journal of Solid-State Circuits, 36(7), 1082–1086.

Ferreira, L. H., & Sonkusale, S. R. (2014). A 60-dB gain OTA operating at 0.25-V power supply in 130-nm digital CMOS process. IEEE Transactions on Circuits and Systems I: Regular Papers, 61(6), 1609–1617.

Veldandi, H., & Shaik, R. A. (2018). A 0.3-V pseudo-differential bulk-input OTA for low-frequency applications. Circuits, Systems, and Signal Processing, 37(12), 5199–5221.

Tsividis, Y., & McAndrew, C. (2011). Operation and modeling of the MOS transistor. Oxford University Press.

Razavi, B. (2002). Design of analog CMOS integrated circuits. Tata McGraw-Hill Education.

Rashtian, H. (2013). On the use of body biasing to improve the performance of CMOS RF front-end building blocks (Doctoral dissertation, University of British Columbia).

Akbari, M., Nazari, M., Sharifi, L., & Hashemipour, O. (2015). Improving power efficiency of a two-stage operational amplifier for biomedical applications. Analog Integrated Circuits and Signal Processing, 84(2), 173–183.

Magnelli, L., Amoroso, F. A., Crupi, F., Cappuccino, G., & Iannaccone, G. (2014). Design of a 75-nW, 0.5-V subthreshold complementary metal–oxide–semiconductor operational amplifier. International Journal of Circuit Theory and Applications, 42(9), 967–977.

Anisheh, S. M., Abbasizadeh, H., Shamsi, H., Dadkhah, C., & Lee, K. Y. (2019). 84 dB DC-gain two-stage class-AB OTA. IET Circuits, Devices & Systems, 13(5), 614–621.

Centurelli, F., Monsurrò, P., & Trifiletti, A. (2019). High-gain, high-CMRR class AB operational transconductance amplifier based on the flipped voltage follower. International Journal of Circuit Theory and Applications, 47(4), 499–512.

Wang, J., Li, Y., & Zhu, Z. (2019). A 0.6-V pseudo-differential OTA with switched-opamp technique for low power applications. Microelectronics Journal, 90, 117–122.

Cellucci, D., Centurelli, F., Di Stefano, V., Monsurrò, P., Pennisi, S., Scotti, G., & Trifiletti, A. (2020). 0.6-V CMOS cascode OTA with complementary gate-driven gain-boosting and forward body bias. International Journal of Circuit Theory and Applications, 48(1), 15–27.

Aghaee, T., Biabanifard, S., & Golmakani, A. (2017). Gain boosting of recycling folded cascode OTA using positive feedback and introducing new input path. Analog Integrated Circuits and Signal Processing, 90(1), 237–246.

Garde, M. P., Lopez-Martin, A., Algueta, J. M., Carvajal, R. G., & Ramirez-Angulo, J. (2019). Class AB amplifier with enhanced slew rate and GBW. International Journal of Circuit Theory and Applications, 47(8), 1199–1210.

Khade, A. S., Vyas, V., Sutaone, M., & Musale, S. (2019). Transconductance enhancement of a low voltage low power recycling folded cascode OTA using an asymmetrical current split input stage. Microelectronics Journal, 91, 53–60.

Centurelli, F., Fava, A., Olivieri, M., Tommasino, P., & Trifiletti, A. (2020). A low-voltage class-AB OTA exploiting adaptive biasing. AEU-International Journal of Electronics and Communications, 153282.

Sabry, M. N., Omran, H., & Dessouky, M. (2018). Systematic design and optimization of operational transconductance amplifier using gm/ID design methodology. Microelectronics Journal, 75, 87–96.

Flandre, D., Jespers, P., & Silveira, F. (1996). A gm/ID based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on-insulator micropower OTA. IEEE Journal of Solid-State Circuits, 31(9), 1314–1319.

Fakhfakh, M., Cooren, Y., Sallem, A., Loulou, M., & Siarry, P. (2010). Analog circuit design optimization through the particle swarm optimization technique. Analog Integrated Circuits and Signal Processing, 63(1), 71–82.

Bachir, B., Ali, A., & Abdellah, M. (2012). Multiobjective optimization of an operational amplifier by the ant colony optimisation algorithm. Electrical and Electronic Engineering, 2(4), 230–235.

Figueiredo, M., Santos-Tavares, R., Santin, E., Ferreira, J., Evans, G., & Goes, J. (2011). A two-stage fully differential inverter-based self-biased CMOS amplifier with high efficiency. IEEE Transactions on Circuits and Systems I: Regular Papers, 58(7), 1591–1603.

Ghosh, S., De, B. P., Kar, R., & Mal, A. K. (2019). Symbiotic organisms search algorithm for optimal design of CMOS two-stage op-amp with nulling resistor and robust bias circuit. IET Circuits, Devices & Systems, 13(5), 679–688.

Acknowledgements

This work has been performed using the VLSI laboratory resources developed under the Special Manpower Development Program for VLSI design and related software (SMDP-II) project funded by Department of Information Technology, Government of India at MNNIT Allahabad, Prayagraj, UP.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that there is no conflict of interest regarding the publication of this work.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Ghosh, S., Bhadauria, V. An ultra-low-power near rail-to-rail pseudo-differential subthreshold gate-driven OTA with improved small and large signal performances. Analog Integr Circ Sig Process 109, 345–366 (2021). https://doi.org/10.1007/s10470-021-01899-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01899-8