Abstract

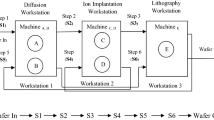

The complex process and high variation in wafer fabrication make its production management very difficult. Problems such as planned target achievement and line balancing are not unusual in the industry. Such problems reveal the importance of develo** a daily production policy for wafer fabrication. Planned target achievement and line balancing are the major concerns of this investigation in develo** a daily production model. This investigation divides the process of wafer fabrication into two sections, i.e., the front and the rear, according to the last sputtering operation step. In the rear section, the objective is attaining the planned output target. In the front section, the major focus is to satisfy the demand of the rear section so that the production line is balanced. Release and dispatch policies are incorporated in this study to achieve both objectives. A real-world numerical example is used as simulation data. Results show that the proposed daily production model gives a better performance in the achievement of monthly planned output but suffers a little in the performance of line balancing.

Similar content being viewed by others

References

Burman DY, Gurrola-Gal FJ, Nozari A, Sathaye S, Sitarik JP (1986) Performance analysis techniques for IC manufacturing lines. AT & T Tech J 65(4):46–57

Chan WS (1997) A relationship model for production performance indices in wafer fabrication factories. Master Thesis, National Chiao Tung University, Hsin-chu, Taiwan

Cheng CM (1996) The design of a due date assignment model for a wafer fabrication factory. Master Thesis, National Chiao Tung University, Hsin-chu, Taiwan

Chang SC, Lee LH, Pang LS, Chang YC, Lin PC, Chen TWY (1992) Daily target generation and machine allocation for integrated circuit fabrication. In: The Second International Conference on Automation Technology 4:47–52

Glassey CR, Resende MGC (1988) Closed-loop job release control for VLSI circuit manufacturing. In: IEEE Transactions on Semiconductor Manufacturing 1:36–46

Glassey CR, Resende MGC (1988) A scheduling rule for job release in semiconductor fabrication. Oper Res Letters 7:213–217

Graves RJ, Konopka JM, Milne RJ (1995) Literature review of material flow control mechanisms. Prod Plann Control 6(5):395–403

Kager PW, Lou S (1989) A robust production control policy for VLSI wafer fabrication. In: IEEE Transactions on Semiconductor Manufacturing 2:159–164

Lawton JW (1990) Workload regulating wafer release in a GaAa fab facility. In: International Semiconductor Manufacturing Science Symposium, pp. 33–38

Lee KJ (1995) The construction of a production planning system for wafer fabrication factories. Master Thesis, National Chiao Tung University, Hsin-chu, Taiwan

Li S, Tom T, Donald CW (1996) Minimum inventory variability schedule with applications in semiconductor fabrication. IEEE Transactions on Semiconductor Manufacturing 9:145–149

Lin Y-H, Lee C-E (2001) A total standard WIP estimation method for wafer fabrication. Eur J Oper Res 131:78–94

Lou SXC (1989) Optimal control rules for scheduling job shops. Ann Oper Res 17:233–248

Lou SXC, Kager PW (1989) A robust production control policy for VLSI wafer fabrication. In: IEEE Transactions on Semiconductor Manufacturing 2(4):159–164

Miller DJ (1990) Simulation of a semiconductor manufacturing line. ACM 33(10):99–108

Roderick LM, Philips DT, Hogg GL (1992) A comparison of order release strategies in production control systems. Int J Prod Res 30(3):611–626

Wang TH (1994) Design and analysis of a short term scheduling method for semiconductor manufacturing. Master Thesis, National Taiwan University, Taipei, Taiwan

Wein LM (1988) Scheduling semiconductor wafer fabrication. In: IEEE Transactions on Semi-conductor Manufacturing 1(3)115–130

Yan HS, Lou SS, Gardel A, Deosthali P (1996) Testing the robustness of two-boundary control policies in semiconductor manufacturing. In: IEEE Transactions on Semiconductor Manufacturing 9(2):285–288

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Pai, PF., Lee, CE. & Su, TH. A daily production model for wafer fabrication. Int J Adv Manuf Technol 23, 58–63 (2004). https://doi.org/10.1007/s00170-002-1506-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00170-002-1506-9