Abstract

This chapter introduces the critical steps involved in fabricating through-silicon vias (TSVs) and associated materials. The fabrication steps for TSVs begin with etching of high aspect ratio trenches in Si, followed by placement of dielectric, barrier and seed layers, TSV filling and polishing, and then assembly with other components of a device. In addition, planarization, die-thinning and flow processes to fabricate TSV-enabled 3-D architectured microelectronic package are described. Challenges associated with processing of TSVs as well as methods for overcoming them are highlighted and discussed.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

Notes

- 1.

Layout efficiency is understood as the number of conductors per unit area.

- 2.

KOZ is the region where functional properties of Si are significantly affected by the stress field of the TSV.

References

E. Beyne, Through-silicon via technology for 3D IC, in: Ultra-Thin Chip Technology and Applications, ed. by J.N. Burghartz (Springer, New York, 2011)

M. Stucchi, G. Katti, D. Velenis, TSV characterization and modeling, in: Three Dimensional System Integration: IC Stacking Process and Design, ed. by A. Papanikolaou, D. Soudris, R. Radojcic (Springer, New York, 2011)

P.S. Andry, C.K. Tsang, B.C. Webb, E.J. Sprogis, S.L. Wright, B. Dang, D.G. Manzer, Fabrication and characterization of robust through-silicon vias for silicon-carrier applications. IBM J. Res. Dev. 52, 571–581(2008)

Z. Xu, J.Q. Lu, High-speed design and broadband modeling of through-strata-vias (TSVs) in 3D integration. IEEE Trans. Compon. Pack. Manuf. Technol. 1, 154–162 (2011)

J.Q. Lu, Advances in materials and processes for 3D-TSV integration. ECS Trans. 45, 119–129 (2012)

A. Tsukada, R. Sato, S. Sekine, R. Kimura, K. Kishi, Y. Sato, Y. Iwata, H. Murata, Study on TSV with new filling method and alloy for advanced 3D-SiP, in: ECTC: Electronic Components and Technology Conference, 31 May–3 June 2011, Lake Buena Vista, FL, New York, USA (IEEE, 2011), p. 1981

R. Sato, A.Tsukada, Y. Sato, Y. Iwata, H. Murata, S. Sekine, R. Kimura, K. Kishi, Study on high performance and productivity of TSV’s with new filling method and alloy for advanced 3D-SiP, in: 3DIC: International 3D Systems Integration Conference, 31 Jan–2 Feb 2012, Osaka, New York, USA (IEEE, 2012), p. 1

A. Horibe, K. Sueoka, T. Aoki, K. Toriyama, K. Okamoto, S. Kohara, H. Mori, Y. Orii, Through silicon via process for effective multi-wafer integration, in: ECTC: Electronic Components and Technology Conference, 26–29 May 2015, San Diego, CA (IEEE, 2015), p. 1808

M. Bouchoucha, L.L. Chapelon, P. Chausse, S. Moreau, N. Sillon, Through silicon via polymer filling for 3D-WLP applications, in: ESTC: Electronic System-Integration Technology Conference, 13–16 Sept 2010, Berlin (IEEE, 2010), p. 1

A. Peic, Lithography Process Innovations for 2.5/3D Part 1: Alleviating TSV Stress (2014), http://www.3dincites.com/2014/08/lithography-process-innovations-for-2-53d-part-1-alleviating-tsv-stress/. Accessed 21 June 2016

L. Zhu, D.W. Hess, C.P. Wong, Carbon nanotube electrical and thermal properties and applications for interconnects, in: Integrated Interconnect Technologies for 3D Nanoelectronic Systems, ed. by M.S. Bakir, J.D. Meindl (Artech House, Norwood, MA, 2009)

D. Jiang, W. Mu, S. Chen, Y. Fu, K. Jeppson, J. Liu, Vertically stacked carbon nanotube-based interconnects for through silicon via application. IEEE Electron Dev. Lett. 36, 499–501 (2015)

J.U. Knickerbocker, P.S. Andry, B. Dang, et al., Three dimensional silicon integration. IBM J. Res. Dev. 52, 553–569 (2008)

J.Q. Lu, 3-D hyperintegration and packaging technologies for micro-nano systems. Proc. IEEE 97, 18–30 (2009)

M. Koyanagi, T. Fkushima, T. Tanaka, High-density through silicon vias for 3-D LSIs. Proc. IEEE 97, 49–59 (2009)

S Spiesshoefer, Z. Rahman, G. Vangara, S. Polamreddy, S. Burkett, L. Schaper, Process integration for through-silicon vias. J. Vac. Sci. Technol. A 23, 824–829 (2005)

R. Nagarajan, K. Prasad, L. Ebin, B. Narayanan, Development of dual-etch via tapering process for through-silicon interconnection. Sens. Actuators A 139, 323–329 (2007)

R. Li, Y. Lamy, W.F.A. Besling, F. Roozeboom, P.M. Sarro, Continuous deep reactive ion etching of tapered via holes for three-dimensional integration. J. Micromech. Microeng. 18, 125023 (2008)

C. Okoro, K. Vanstreels, R. Labie, O. Luhn, B. Vandevelde, B. Verlinden, D. Vandepitte, Influence of annealing conditions on the mechanical and microstructural behavior of electroplated Cu-TSV. J. Micromech. Microeng. 20, 045032 (2010)

N. Ranganathan, L. Ebin, L. Linn, L.W.S. Vincent, O.K. Navas, V. Kripesh, N. Balasubramanian, Integration of high aspect ratio tapered silicon via for silicon carrier fabrication. IEEE Trans. Adv. Pack. 32, 62–71 (2009)

B. Wu, A. Kumar, S. Pamarthy, High aspect ratio silicon etch: a review. J. Appl. Phys. 108, 051101 (2010)

D. Gerke, NASA 2009 body of knowledge (BoK): through-silicon via technology. JPL Publication 09-28, Jet Propulsion Laboratory, Pasadena, CA (2009)

R. Landgraf, R. Rieske, A.N. Danilewsky, K.J. Wolter, Laser drilled through silicon vias: crystal defect analysis by synchrotron X-ray topography, in: ESTC: 2nd Electronics System-Integration Technology Conference, Greenwich, New York, USA 1–4 Sept 2008 (IEEE, 2008), p. 1023

Y.H. Lee, K.J. Choi, Analysis of silicon via hole drilling for wafer level chip stacking by UV laser. Int. J. Prec. Eng. Manuf. 11, 501–507 (2010)

Industrial laser application note: laser drilling of through silicon vias (tsv). http://www.spectra-physics.com/applications/application-notes/laser-drilling-of-through-silicon-vias-tsv. Accessed 21 June 2016

A. Polyakov, T. Grob, R.A. Hovenkamp, H.J. Kettelarij, I. Eidner, M.A. de Samber, M. Bartek, J.N. Burghartz, Comparison of via-fabrication techniques for through-wafer electrical interconnect applications, in: ECTC: Electronic Components and Technology Conference, 1–4 June 2004 (IEEE, 2004), p. 1466

S.P. Lee, H.-W. Kang, S.-J. Lee, I.H. Lee, T.J. Ko, D.-W. Cho, Development of rapid mask fabrication technology for micro-abrasive jet machining. J. Mech. Sci. Technol. 22, 2190–2196 (2008)

M.J. Archer, F.S. Ligler, Fabrication and characterization of silicon micro-funnels and tapered micro-channels for stochastic sensing applications. Sensors 8, 3848–3872 (2008)

S.H. Kim, et al. (1 1 0) Silicon etching for high aspect ratio comb structures, in: ETFA’97: Proc. Emerging Technologies and Factory Automation, 9–12 Sept 1997, Los Angeles, CA (IEEE, 1997), p. 248

G.T.A. Kovacs, N.I. Maluf, K.E. Petersen, Bulk micromachining of silicon. Proc. IEEE 86, 1536–1551 (1998)

S. Aachboun, P. Ranson, Deep anisotropic etching of silicon. J. Vac. Sci. Technol. A 17, 2270–2273 (1999)

F. Laermer, A. Schilp, Method of anisotropically etching silicon. US Patent US5501893 A (1996)

M.J. Madou, Fundamentals of Microfabrication: The Science of Miniaturization, 2nd ed. (CRC Press, Boca Raton, 2002)

P. Nallan, A. Khan, S. Pamarthy, S.T. Hsu, A. Kumar, Advanced deep silicon etching for deep trench isolation, optical components and micro-machining applications, in: ET Conference Proceedings (Applied Materials Internal Publication, 2001), Santa Clara, USA

S.-B. Jo, M.-W. Lee, S.-G. Lee, E.-H. Lee, S.-G. Park, B.-H. O, Characterization of a modified Bosch-type process for silicon mold fabrication. J. Vac. Sci. Technol. A 23, 905–910 (2005)

M.J. Walker, Comparison of Bosch and cryogenic processes for patterning high aspect ratio features in silicon. Proc. SPIE 4407, 89–99 (2001)

I.R. Johnston, H. Ashraf, J.K. Bhardwaj, J. Hopkins, A.M. Hynes, G. Nicholls, S.A. McAuley, S. Hall, L. Atabo, G.R. Bogart, A. Kornblit, A.E. Novembre, Etching 200-mm diameter SCALPEL masks with the ASE process. Proc. SPIE 3997, 184–193 (2000)

R. Nagarajan, L. Ebin, D. Lee, C.S. Soh, K. Prasad, N. Balasubramanian, Development of a novel deep silicon tapered via etch process for through-silicon interconnection in 3-D integrated systems, in: ECTC: Electronic Components and Technology Conference, 30 May–2 June 2006, San Diego, CA (IEEE, 2006), p. 383

J.-H. Lai, H.S. Yang, H. Chen, C.R. King, J. Zaveri, R. Ravindran, M.S. Bakir, A ‘mesh’ seed layer for improved through-silicon-via fabrication. J. Micromech. Microeng. 20, 025016 (2010)

M. Miao, Y. Zhu, M. Ji, J. Ma, X. Sun, Y. **, Bottom-up filling of through silicon via (TSV) with Parylene as sidewall protection layer, in: EPTC’09: Electronics Packaging Technology Conference, 9–11 Dec 2009, Singapore (IEEE, 2009), p. 442

D.S. Tezcan, F. Duval, H. Philipsen, O. Luhn, P. Soussan, B. Swinnen, Scalable through silicon via with polymer deep trench isolation for 3D wafer level packaging, in: ECTC: Electronic Components and Technology Conference, 26–29 May 2009, San Diego, CA, New York, USA (IEEE, 2009), p. 1159

P. Shi, J. Enloe, R. van den Boom, B. Sapp, Direct copper electrodeposition on a chemical vapor-deposited Ruthenium seed layer for through-silicon vias, in: IITC: International Interconnect Technology Conference, 4–6 June 2012, San Jose, CA (IEEE, 2012), p. 1

M.J. Wolf, T. Dretschkow, B. Wunderle, N. Jurgensen, G. Engelmann, O. Ehrmann, A. Uhlig, B. Michel, H. Reichl, High aspect ratio TSV copper filling with different seed layers, in: ECTC: Electronic Components and Technology Conference, 27–30 May 2008, Lake Buena Vista, FL (IEEE, 2008), p. 563

V.S. Rao, S.W. Ho, W.S.V. Lee, H.Y. Li, E. Liao, R. Nagarajan, T.C. Chai, X. Zhang, P. Damaruganath, TSV interposer fabrication for 3D IC packaging, in: EPTC’09: Electronics Packaging Technology Conference, 9–11 Dec 2009, Singapore (IEEE, 2009), p. 431

Y. Au, Q.M. Wang, H. Li, J.S.M. Lehn, D.V. Shenai, R.G. Gordon, Vapor deposition of highly conformal copper seed layers for plating through-silicon vias (TSVs). J. Electrochem. Soc. 159, D382–D385 (2012)

P.H. Haumesser, L.A. Roule, S. Maitrejean, G. Passemard, Seed enhancement: a bridging technology. Future Fab. Intl. 19, 81–83 (2005)

K.J. Ganesh, A.D. Darbal, S. Rajasekhara, Effect of downscaling nano-copper interconnects on the microstructure revealed by high resolution TEM-orientation-map**. Nanotechnology 23, 135702 (2012)

T.P. Moffat, D. Josell, Extreme bottom-up superfilling of through-silicon-vias by damascene processing: suppressor disruption, positive feedback and Turing patterns. J. Electrochem. Soc. 159, D208–D216 (2012)

J. Dukovic, S. Ramaswami, S. Pamarthy, R. Yalamanchili, N. Rajagopalan, K. Sapre, Z. Cao, T. Ritzdorf, Y. Wang, B. Eaton, R. Ding, M. Hernandez, M. Naik, D. Mao, J. Tseng, D. Cui, G. Mori, P. Fulmer, K. Sirajuddin, J. Hua, S. **a, D. Erickson, R. Beica, E. Young, P. Kusler, R. Kulzer, S. Oemardani, H. Dai, X. Xu, M. Okazaki, K. Dotan, C. Yu, C. Lazik, J. Tran, L. Luo, Through-silicon-via technology for 3D integration, in: IEEE International Memory Workshop, 16–19 May 2010, Seoul (IEEE, 2010), p. 1

B. Horvath, J. Kawakita, T. Chikyow, Through silicon via filling methods with metal/polymer composite for three-dimensional LSI. Jpn. J. Appl. Phys. 53, 06JH01 (2014)

P. Dixit, T. Vehmas, S. Vahanen, P. Monnoyer, K. Henttinen, Fabrication and electrical characterization of high aspect ratio poly-silicon filled through-silicon vias. J. Micromech. Microeng. 22, 055021 (2012)

C.-F. Hsu, W.-P. Dow, H.-C. Chang, W.-Y. Chiu, Optimization of the copper plating process using the Taguchi experimental design method: I. Microvia filling by copper plating using dual leverlers. J. Electrochem. Soc. 162, D525–D530 (2015)

G. Pares, N. Bresson, S. Minoret, V. Lapras, P. Brianceau, J.F. Lugand, R. Anciant, N. Sillon, Through silicon via technology using tungsten metallization, in: ICICDT: International Conference IC Design & Technology, 2–4 May 2011, Kaohsiung (IEEE, 2011), p. 1

R.L. Rhoades, Overview of CMP for TSV applications (2013), http://www.entrepix.com/docs/papers-and-presentations/Rhoades-CMP-for-TSV-AVS-June2013-shareable.pdf. Accessed 21 June 2016

S.W. Yoon, D.J. Na, K.T. Kang, W.K. Choi, C.B. Yong, Y.C. Kim, P.C. Marimuthu, TSV MEOL (Mid-End-Of-Line) and its assembly/packaging technology for 3D/2.5D solutions, in: ICEP-IAAC: Joint Conference of International Conference on Electronics Packaging and IMAPS All Asia Conference, 17–20 April 2012, Tokyo (2012), http://www.statschippac.com/~/media/Files/DocLibrary/whitepapers/2012/STATSChipPAC_ICEP2012_TSV_MEOL_and_Pkg.ashx. Accessed 21 June 2016

D. Smith, S. Singh, Y. Ramnath, M. Rabie, D. Zhang, L. England, TSV residual Cu step height analysis by white light interferometry for 3D integration, in: ECTC: Electronic Components and Technology Conference, 26–29 May 2015, San Diego, CA (IEEE, 2015), p. 578

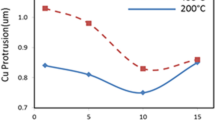

A. Heryanto, W.N. Putra, A. Trigg, S. Gao, W.S. Kwon, F.X. Che, X.F. Ang, J. Wei, R.I. Made, C.L.Gan, K.L. Pey, Effect of copper TSV annealing on via protrusion for TSV wafer fabrication. J. Electron Mater. 41, 2533–2542 (2012)

T. Jiang, S.-K. Ryu, Q. Zhao, J. Im, R. Huang, P.S. Ho, Measurement and analysis of thermal stresses in 3D integrated structures containing through-silicon-vias. Microelectron Reliab. 53, 53–62 (2013)

K. Ohta, A. Hirate, Y. Miyachi, T. Shimizu, S. Shingubara, All-wet TSV filling with highly adhesive displacement plated Cu seed layer, in: 3DIC: International 3D Systems Integration Conference, 31 Aug–2 Sept 2015, Sendai, New York, USA (IEEE, 2015), p. TS8.4.1

Q. Cui, X. Sun, Y. Zhu, S. Ma, J. Chen, M. Miao, Y. **, Design and optimization of redistribution layer (RDL) on TSV interposer for high frequency applications, in: ICEPT-HDP: International Conference on Electronic Packaging Technology and High Density Packaging, 8–11 Aug 2011, Shanghai, New York, USA (IEEE, 2011), p. 1

IBM 3D Semiconductor & Packaging Technology for Systems. http://researcher.ibm.com/researcher/view_group.php?id=4436. Accessed 21 June 2016

Acknowledgements

The editors would like to thank Purushotham Kaushik Muthur Srinath and Shengquan E Ou from Intel Corporation for their critical review of this chapter. The authors (PK and ID) acknowledge financial support for some of the reported work by the National Science Foundation (DMR-0513874 and DMR-1309843), Cisco Research Council and the Semiconductor Research Corporation. PK would also like to acknowledge financial support from Department of Science and Technology, India (grant number DSTO 1164). The contributions of, and collaborations with several colleagues (Dr. Lutz Meinshausen, formerly of Washington State University, and currently at Global Foundries, Dresden, Germany; Dr. Tae-Kyu Lee, formerly of Cisco Systems, and currently at Portland State University; Dr. Ravi Mahajan of Intel Corporation; Dr. Vijay Sarihan of Freescale Semiconductor, and Professor Muhannad Bakir of Georgia Tech) are gratefully acknowledged. The assistance of current and former colleagues (Dr. Hanry Yang of Washington State University, and Dr. Zhe Huang, formerly of Washington State University, and currently at Seagate Technologies) with the literature survey is also gratefully acknowledged. The author (ZH) acknowledges financial support for his research by the Pearl River Science and Technology Nova Program of Guangzhou under grant no. 2012J2200074, the National Natural Science Foundation of China (NSFC) under grant no. 51004118 and Guangdong Natural Science Foundation under grant no. 2015A030312011.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer International Publishing Switzerland

About this chapter

Cite this chapter

Kumar, P., Dutta, I., Huang, Z., Conway, P. (2017). Materials and Processing of TSV. In: Li, Y., Goyal, D. (eds) 3D Microelectronic Packaging. Springer Series in Advanced Microelectronics, vol 57. Springer, Cham. https://doi.org/10.1007/978-3-319-44586-1_3

Download citation

DOI: https://doi.org/10.1007/978-3-319-44586-1_3

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-44584-7

Online ISBN: 978-3-319-44586-1

eBook Packages: EngineeringEngineering (R0)