Abstract

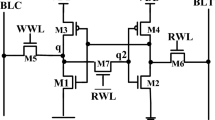

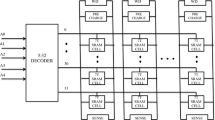

In terms of memory, multivalued logic can be the fitting logic for the existing binary logic. Ternary logic contains three symbols in place of two symbols used in the binary logic, i.e., 0, 1, 2. More information can be stored with the help of these three symbols. SRAM cell is widely used in the digital circuit. The SRAM cell designed using the ternary logic can be used in the design of large memory arrays designed using ternary logic. The traditional ternary inverter which is used in the design of the traditional ternary SRAM cell is unable to store the proper values for the second state, there is a voltage level drop, which in turn affects the data read/write value of the SRAM cell designed using this traditional ternary inverter. Hence there is a need to design the ternary inverter cell which can give the proper output voltage level of all three states of the ternary logic. The level shift ternary inverter is designed to fulfill this disadvantage. The ternary inverter is designed in order to achieve the ideal DC characteristics, and the same level shift ternary inverter is used in the design of level shift ternary SRAM. This ternary SRAM stores the data properly at read/write signal. The traditional ternary inverter and traditional ternary SRAM, level shift ternary inverter and level shift ternary SRAM are implemented in Cadence 45 nm technology. The traditional ternary inverter consumes 2.37 μW power, and the level shift ternary SRAM consumes 2.43 μW power. The traditional ternary SRAM consumes 3.012 μW and level shift ternary SRAM consumes 3.14 μW. At the cost of a little bit increased power and the number of transistors, the traditional ternary SRAM can be replaced with level shift ternary SRAM. This level shift ternary SRAM stores all the voltage levels at all three levels. The same level shift ternary SRAM cell can be used for the design of large memory arrays.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Srinivasa Raghavan B, Kanchana Bhaaskaran VS. Design of novel multiple valued logic (MVL) circuits. In: 2017 International conference on nextgen electronic technologies: silicon to software (ICNETS2), Chennai, India, pp 371–378

Vasundara Patel KS, Gurumurthy KS (2009) Quaternary CMOS combinational logic circuits. In: 2009 international conference on information and multimedia technology, Jeju Island, pp 538–542

Shanmugavadivu P, Sugunadevi S, Sukanya B (2016) Study of static noise margin of SRAM based on supply voltage and topologies. IJAR. ISSN Print 2394-7500, ISSN Online 2394-5869

Srinivasan P, Bhat AS, Murotiya SL, Gupta A (2015) Design and performance evaluation of a low transistor ternary CNTFET SRAM cell. In: 2015 international conference on electronic design, computer networks & automated verification (EDCAV), Shillong, pp 38–43

Moaiyeri MH, Mirzaee RF, Doostaregan A, Navi K, Hashemipour O (2013) A universal method for designing low-power carbon nanotube FET-based multiple valued logic circuits. IET Comput Digital Tech 7(4):167–181

Jahangir MZ, Narasimha KV. Design of a new ternary SRAM cell (ZV-SRAM) based on innovative level shift based ternary inverter (ZV-Inverter). In: Annual India conference (INDICON). IEEE, New Delhi, India, 17–20 Dec 2015

Jayashree HV, Sai Shruthi VP. Ternary SRAM for low power applications. In: International conference on communication, information & computing technology (ICCICT), Mumbai, India, Oct 2012

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Shylashree, N., Hosur, A., Praveena, N. (2019). Design of Ternary SRAM Cell Based on Level Shift Ternary Inverter. In: Sridhar, V., Padma, M., Rao, K. (eds) Emerging Research in Electronics, Computer Science and Technology. Lecture Notes in Electrical Engineering, vol 545. Springer, Singapore. https://doi.org/10.1007/978-981-13-5802-9_79

Download citation

DOI: https://doi.org/10.1007/978-981-13-5802-9_79

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-13-5801-2

Online ISBN: 978-981-13-5802-9

eBook Packages: EngineeringEngineering (R0)