Abstract

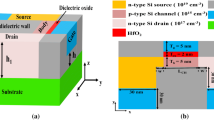

In this paper, N-type and P-Type low power SiGe Silicon on Insulator Vertical TFET (SOI-VTFETs) are designed and then their drain current is investigated. The designed structures are calibrated with the reported structures considering the same model’s environment for the validation of the design. Here, several advantages of SOI have been incorporated so that the low-voltage with low power (LVLP) VLSI designs digital circuits can be easily realized. Gate staking of high k -dielectric (HfO2) material with SiO2 was used to prevent the loss of the Lattice misfit structure using the equivalent oxide thickness approach. The proposed device’s highest ON current and largest ON/OFF current are claimed to be (3.62 × 10−4 A/m) and (1013), respectively. Then the designed device is used to implement the full adder and the Infinite Impulse Response (IIR) filters. It is found that the performance of IIR filters is much enhanced over Finite Impulse Response (FIR) filters to keep flat response for altogether trial rates. The total delay of the IIR decimation filter via Merged Delay Transformation (MDT) is 0.181 ns with a Power Delay Product (PDP) of 3.5767. The current method employs the Routh Hurwitz Array method’s advantages to derive the reduced-order denominator polynomial, and the reduced order numerator is obtained based on the resultant denominator polynomial. This order reduction technique is incorporated to reduce the number of delay units of the IIR filter and modified architecture offering a PDP of 0.22563, with its flat response initiated by SOI VTFET. The current model is productive in lowering area, power consumption, and stability over a specific sample rate or frequency.

Similar content being viewed by others

Data Availability

My manuscript has no associated data.

References

Choi WY, Park B-G, Lee JD, Liu T-JK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Letters 28(8):743–745. https://doi.org/10.1109/LED.2007.901273

Khatami Y, Banerjee K (2009) Steep subthreshold slope n- and p-type tunnel-FET devices for low-power and energy- efficient digital circuits. IEEE Trans Electron Dev 56(11):2752–2760. https://doi.org/10.1109/TED.2009.2030831

Arun Samuel TS, Balamurugan NB, Bhuvaneswari S, Sharmila D, Padmapriya K (2014) Analytical modelling and simulation of single-gate SOI TFET for low-power applications. Int J Electron 101(6):779–788

Chander S, Bhowmick B, Baishya S (2015) Heterojunction fully depleted SOI-TFET with oxide/source overlap. Superlattices and Microstructures 86:43–50

Yasir M, Samar Ansari M, Kumar Sharma V (2018) Performance evaluation of a FinFET-based dual-output second generation current conveyor. In 2018 IEEE 18th International Conference on Nanotechnology (IEEE-NANO), pp. 1–4. IEEE

Yasir M, Hasan M, Samar Ansari M (2018) Two-stage FinFET-MOSFET hybrid inductive boost converter. In 2018 Second International Conference on Inventive Communication and Computational Technologies (ICICCT), pp. 1571–1576. IEEE

Yasir M, Alam N (2021) Design of TFET based Op-amp and CCII for low voltage and low power applications. International Journal of Electronics 108(10):1733–1753

Pandey CK, Dash D, Chaudhury S (2020) Improvement in analog/RF performances of SOI TFET using dielectric pocket. International Journal of Electronics 107(11):1844–1860

Ehteshamuddin M, Loan SA, Rafat M (2018) A vertical-gaussian doped soi-tfet with enhanced dc and analog/rf performance. Semiconductor Science and Technology 33(7):075016

Silvaco, ATLAS User’S. Manual Device. "Simulation Software." Santa Clara CA: Silvaco International 444 (2018)

Ramesh K, Ganesan RG, Mahalakshmi K (2017) Approximation and optimization of discrete systems using order reduction technique. Energy Procedia 117:761–768

Pati A, Kumar A, Chandra D (2014). Suboptimal control using model order reduction. Chinese J Eng, 2014, 1–5

Parmar G, Prasad R, Mukherjee S (2007) Order reduction of linear dynamic systems using stability equation method and GA. Int J Comput Inform Systems Sci Eng 1(1):26–32

Krishnamurthy V, Seshadri V (1978) Model reduction using the Routh stability criterion. IEEE Trans Automatic Control 23(4):729–731

Ramesh K, Nirmalkumar A, Gurusamy G (2009) Design of digital IIR filters with the advantages of model order reduction technique. Int J Electron, Communications Comput Eng 1(2):117–122

Hutton M, Friedland B (1975) Routh approximations for reducing order of linear, time-invariant systems. IEEE Trans Automatic Control 20(3):329–337

Panda S, Tomar SK, Prasad R, Ardil C (2009) Reduction of linear time-invariant systems using Routh-approximation and PSO. Int J Appl Math Comput Sci 5(2):82–89

Shamash Y (1975) Model reduction using the Routh stability criterion and the Padé approximation technique. Int J Control 21(3):475–484

Appiah RK (1978) Linear model reduction using Hurwitz polynomial approximation. Int J Control 28(3):477–488

Sambariya DK, Sharma O (2016) Model order reduction using routh approximation and cuckoo search algorithm. J Automation Control 4(1):1–9

Chen TC, Chang CY, Han KW (1980) Model reduction using the stability-equation method and the Padé approximation method. J Franklin Institute 309(6):473–490

Smitha GL (2017). System generator-based area reduction of IIR decimation filter, International Journal of Innovative Research in Computer and Communication Engineering (IJIRCCE) Vol.5, Issue 6

Zhang C, Wang A (2012) IIR digital filter design research and simulation on MATLAB. International Proceedings of Computer Science and Information Technology 58:138

Liang Y, Chen T, Pan Q (2009) Multi-rate optimal state estimation. Int J Control 82(11):2059–2076

Gardner FM (1993) Interpolation in digital modems. I. Fundamentals. IEEE Transactions on communications 41(3):501–507

Abed KH, Nerurkar SB (2003). Low power and hardware efficient decimation filter. In 2003 IEEE wireless communications and networking, 2003. WCNC 2003. (Vol. 1, pp. 454-459). IEEE

Russell AI (2000) Efficient rational sampling rate alteration using IIR filters. IEEE Signal Processing Letters 7(1):6–7

Sambariya DK, Manohar, H (2016). Model order reduction by differentiation equation method using with routh array method. In 2016 10th international conference on intelligent systems and control (ISCO) (pp. 1-6). IEEE

Prasad R (2000) Pade type model order reduction for multivariable systems using Routh approximation. Computers & Electrical Engineering 26(6):445–459

Prajapati AK, Prasad R (2019) Order reduction of linear dynamic systems by improved Routh approximation method. IETE J Res 65(5):702–715

Parashar D, Sharma MK, Chandel A (2015). Model reduction of discrete interval systems by routh approximation method. In 2015 IEEE Recent Advances in Intelligent Computational Systems (RAICS) (pp. 290–293). IEEE

Narwal A, Prasad R (2015). A novel order reduction approach for LTI systems using cuckoo search and Routh approximation. In 2015 IEEE International Advance Computing Conference (IACC) (pp. 564–569). IEEE

Hsieh CS, Hwang C (1989). Model reduction of continuous-time systems using a modified Routh approximation method. In IEE Proceedings D-Control Theory and Applications (Vol. 136, No. 4, pp. 151-156). IET

Chen TC, Chang CY, Han KW (1980) Model reduction using the stability-equation method and the Padé approximation method. Journal of the Franklin Institute 309(6):473–490

Sambariya DK, Rajawat AS (2016). Model order reduction of lti system using routh stability array method. In 2016 international conference on computing, communication and automation (ICCCA) (pp. 896-901). IEEE

Farooq U, Jamal H, Khan SA (2007). Realization of IIR decimation filters based on merged delay transformation. Journal of Electrical and Computer Engineering, 2007

Mehrmann V, Stykel T (2005) Balanced truncation model reduction for large-scale systems in descriptor form. In dimension reduction of large-scale systems. Springer, Berlin, Heidelberg, pp 83–115

Koswatta SO, Lundstrom MS, Nikonov DE (2009) Performance comparison between pin tunneling transistors and conventional MOSFETs. IEEE Transactions on Electron Devices 56(3):456–465. https://doi.org/10.1109/TED.2008.2011934

Nigam K, Kondekar P, Sharma D (2016) High frequency performance of dual metal gate vertical tunnel field effect transistor based on work function engineering. Micro & Nano Letters 11(6):319–322

Author information

Authors and Affiliations

Contributions

I have equally participated in the preparing of the manuscript during implementation of ideas, findings result, and writing of the manuscript.

Corresponding author

Ethics declarations

Consent to Participate

Not applicable.

Consent for Publication

Not applicable.

Conflict of Interest

The authors declare that there are no conflicts of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Penumutchi, B., Maddu, K. & Kaparapu, B. Design and Application of Silicon on Insulator Based SiGe VTFET in IIR Filter by Balanced Truncation (BT) Method of Model Order Reduction. Silicon 15, 1429–1442 (2023). https://doi.org/10.1007/s12633-022-02086-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-02086-8