Abstract

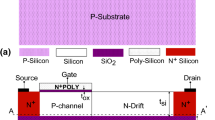

In this paper, a new method is investigated to improve the breakdown voltage in the lateral power MOSFET transistors. The structure is based on Double Buried Metal Layers in the Lateral Diffused MOSFET and it is called DBML-LDMOSFET. The metal layers in the buried oxide under the drift region cause the electric field to be more uniform than the conventional structure. In the DBML-LDMOSFET Structure, the breakdown voltage is improved 25% compared to conventional structure and also the specific on-resistance is almost 11.32 mΩ.cm2. In order to investigate the performance of the structures, SILVACO-ATLAS software has been used and the results have been extracted.

Similar content being viewed by others

References

Chang Y-H, Lin S-W, Chang C-H (2010) Optimization of high voltage LDMOSFETs with complex multiple-resistivity drift region and field plate. Microelectron Reliab 50(7):949–953

Orouji AA, Moghadam HA, Dideban A (2010) Double window partial SOI-LDMOSFET: A novel device for breakdown voltage improvement. Phys E Low-Dimensional Syst Nanostruct 43(1):498–502

Qiao M, Wang Y, Li Y, Zhang B, Li Z (2014) Design of a 1200-V ultra-thin partial SOI LDMOS with n-type buried layer. Superlattice Microst 75:796–805

Orouji AA, Mahabadi SEJ, Keshavarzi P (2011) A novel partial SOI LDMOSFET with a trench and buried P layer for breakdown voltage improvement. Superlattice Microst 50(5):449–460

Anvarifard MK (2018) An impressive structure containing triple trenches for RF power performance (TT-SOI-MESFET). J Comput Electron 17(1):230–237

Anvarifard MK (2017) Creation of a new high voltage device with capable of enhancing driving current and breakdown voltage. Mater Sci Semicond Process 60:60–65

Bao M, Wang Y (2017) Improving breakdown voltage and self-heating effect for SiC LDMOS with double L-shaped buried oxide layers. Superlattice Microst 102:147–154

Yuan S, Duan B, Cao Z, Guo H, Yang Y (2016) Analytical model of LDMOS with a double step buried oxide layer. Solid State Electron 123:6–14

Chen Y et al (2016) A novel low specific on-resistance double-gate LDMOS with multiple buried p-layers in the drift region based on the Silicon-On-Insulator substrate. Superlattice Microst 89:59–67

Duan B, Yuan S, Cao Z, Yang Y (2014) New superjunction LDMOS with the complete charge compensation by the electric field modulation. IEEE Electron Device Lett 35(11):1115–1117

Zareiee M (2019) A new structure for lateral double diffused MOSFET to control the breakdown voltage and the on-resistance. Silicon 11(6):3011–3019

Mehrad M, Zareiee M, Orouji AA (2017) Controlled kink effect in a novel high-voltage LDMOS transistor by creating local minimum in energy band diagram. IEEE Trans Electron Devices 64(10):4213–4218

Duan B, Zhang B, Li Z (2006) New thin-film power MOSFETs with a buried oxide double step structure. IEEE Electron Device Lett 27(5):377–379

Luo X et al (2009) A high-voltage LDMOS compatible with high-voltage integrated circuits on p-type SOI layer. IEEE Electron Device Lett 30(10):1093–1095

Luo X et al (2010) Numerical and Experimental Investigation on a Novel High-Voltage ($> $600-V) SOI LDMOS in a Self-Isolation HVIC. IEEE Trans Electron Devices 57(11):3033–3043

Wang Z, Zhang B, Fu Q, **e G, Li Z (2012) An L-shaped trench SOI-LDMOS with vertical and lateral dielectric field enhancement. IEEE Electron Device Lett 33(5):703–705

Luo X, Zhang B, Li Z, Guo Y, Tang X, Liu Y (2007) A novel 700-V SOI LDMOS with double-sided trench. IEEE Electron Device Lett 28(5):422–424

Luo X et al (2011) Ultralow specific on-resistance high-voltage SOI lateral MOSFET. IEEE Electron Device Lett 32(2):185–187

Yang F-J et al (2013) A 700-V device in high-voltage power ICs with low on-state resistance and enhanced SOA. IEEE Trans Electron Devices 60(9):2847–2853

Zareiee M, Salami H (2018) Inserting PN junction in a power device for achieving improved figure of merit. In: 2018 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), pp 1–4

Kim IJ, Matsumoto S, Sakai T, Yachi T (1994) Breakdown voltage improvement for thin-film SOI power MOSFET’s by a buried oxide step structure. IEEE Electron Device Lett 15(5):148–150

Orouji AA, Sharbati S, Fathipour M (2009) A new partial-SOI LDMOSFET with modified electric field for breakdown voltage improvement. IEEE Trans Device Mater Reliab 9(3):449–453

Silvaco I (2010) ATLAS user’s manual device simulation software, St. Clara, CA

Shockley W, Read WT Jr (1952) Statistics of the recombinations of holes and electrons. Phys Rev 87(5):835

Selberherr S (2012) Analysis and simulation of semiconductor devices. Springer Science & Business Media, Berlin

Zhang B, Wang W, Chen W, Li Z, Li Z (2009) High-voltage LDMOS with charge-balanced surface low on-resistance path layer. IEEE Electron Device Lett 30(8):849–851

Chen W, Zhang B, Li Z (2006) SJ-LDMOS with high breakdown voltage and ultra-low on-resistance. Electron Lett 42(22):1314–1315

Rub M et al (2006) A 600V 8.7 Ohmmm 2 lateral superjunction transistor. In: 2006 IEEE International Symposium on Power Semiconductor Devices and IC’s, pp 1–4

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Shokouhi Shoormasti, A., Abbasi, A. & Orouji, A.A. Improvement the Breakdown Voltage and the On-resistance in the LDMOSFET: Double Buried Metal Layers Structure. Silicon 13, 2157–2164 (2021). https://doi.org/10.1007/s12633-020-00684-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00684-y