Abstract

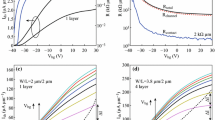

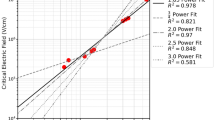

Lateral Double Diffused Metal Oxide Field Effect Transistor (LDMOS) are widely used in power applications for the high breakdown voltage. However, the device may have high on-resistance. So, the challenge for achieving high breakdown voltage and small on-resistance is important. In this paper, a new structure is proposed to enhance the conventional LDMOS performance. In this case, a U-shape P silicon layer is considered in bottom of the drift region and under the gate. The P layer has higher do** density than the drift region which is different from the channel and source/drain. This difference creates some new peaks in the electric field profile decreasing the main peaks. Therefore, the breakdown voltage significantly increases. The on-resistance is reduced when the do** density increases. The higher do** density of P layer than drift region reduces the on-resistance. The paper is simulated using two dimensional ATLAS simulator and is compared to the conventional one. The simulation results show that the proposed structure performance is acceptable in case of electric voltage, breakdown voltage, on-resistance and switching characteristics.

Similar content being viewed by others

References

Yokoyama N, Mimura T, Fukuta M (1980) Planar GaAs MOSFET integrated logic. IEEE Trans. Electron Devices 27:1124–1128

Crawford RH (1967) Capacitive feed through calculations in MOSFET IC's. Proc IEEE 55:1221–1222

Elmasry MI (1981) Digital MOS integrated circuits. IEEE Press, New York

Orouji AA, Anvarifard MK (2013) SOI MOSFET with an insulator region (IR-SOI): a novel device for reliable nanoscale CMOS circuits. Mater Sci Eng B 178:431–437

Anvarifard MK (2016) Increase in the scattering of electric field lines in a new high voltage SOI MESFET. Superlattice Microst 97:15–27

Elmasry MI (1982) Capacitance calculations in MOSFET VLSI. IEEE Electron Device Lett 3:6–7

Taur Y, Ning TH (2013) Fundamentals of modern VLSI devices. Cambridge university press

Cristoloveanu S (2001) Silicon on insulator technologies and devices: from present to future. Solid State Electron 45:1403–1411

Colinge J.P. (2004) Silicon-on-insulator technology: materials to VLSI, 3rd edition. Kluwer Academic Publishers, Boston

Arnold E (1994) Silicon-on-insulator devices for high voltage and power IC applications. J Electrochem Soc 141:1983–1988

Choi H, Shung KK (2014) Novel power MOSFET based expander for high frequency ultrasound systems. Ultrasonics 54:121–113

W-So S, Y-Ho S, S-Young C (2003) SOI RESURF LDMOS transistor using trench filled with oxide. Electron Lett 39:1–2

Lu H, Andre C, Salama T. (2003) A 2 GHz, 60 V-class, SOI power LDMOSFET for base station applications, In Proc. IEEE 15th Int. Symp. ISPSD, pp. 270–273

Bawedin M, Renaux C, Flandre D (2004) LDMOS in SOI technology with very-thin silicon film. Solid State Electron 48:2263–2270

Luo X, Zhang B, Li Z, Guo Y, Tang X, Liu Y (2007) A novel 700-V SOI LDMOS with double-sided trench. IEEE Electron Device Letter 28:422–424

Saremi M, Ebrahimi B, Afzali-kusha A, Mohammadi S (2011) A partial-SOI LDMOSFET with triangle buried-oxide for breakdown voltage improvement. Microelectron Reliab 51:2069–2076

Cheng X, Song Z, Dong Y, Yu Y, Shen D (2005) Patterned silicon-on-insulator technology for RF power LDMOSFET. Microelectron Eng 81:150–155

Saremi M, Saremi M, Niazi H, Saremi M, Goharrizi AY (2017) SOI LDMOSET with up and down extended stepped drift region. J Electron Mater 46:5570–5576

Zareiee M, Orouji AA, Mehrad M (2016) A novel high breakdown voltage LDMOS by protruded silicon dioxide at the drift region. J Comput Electron 15:611–618

Atlas User’s Manual (2012) Santa Clara: Silvaco International

Tao A, Yong G (2007) Breakdown voltage analysis of SOI LDMOS with step buried oxide, 8th International Conference on Electronic Measurement and Instruments, China

Cheng X, Song Z, Dong Y, Yu Y, Shen D (2005) Patterned silicon-on-insulator technology for RF power LDMOSFET. Microelectron Eng 81:150–155

Orouji AA, Mehrad M (2012) Breakdown voltage improvement of LDMOSs by charge balancing: an inserted p-layer in trench oxide (IPT-LDMOS). Superlattice Microst 51:412–420

Pak A, Orouji AA A novel laminated gate to improve the on-state resistance of LDMOS transistors. J Comput Electron

Mehrad M (2015) Thin layer oxide in the drift region of laterally double-diffused metal oxide semiconductor on silicon-0n-insulator: a novel device structure enabling reliable high temperature. Mater Sci Semicond Process 30:599–604

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Zareiee, M. A New Structure for Lateral Double Diffused MOSFET to Control the Breakdown Voltage and the On-Resistance. Silicon 11, 3011–3019 (2019). https://doi.org/10.1007/s12633-019-0092-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-0092-5