Abstract

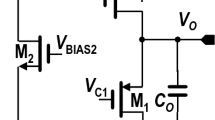

A flipped voltage follower structure based on a dynamic current boosting technique is proposed which enables the fast-transient behavior. It is applied to an output capacitor-less low-dropout (LDO) regulator to improve the output transient response and reduce the over/undershoots of the output voltage when the load current or the input voltage is suddenly changed. The proposed low-dropout regulator is simulated in 0.18 μm CMOS technology, which the output voltage is regulated at 1 V with a dropout voltage of about 114 mV. The output voltage over/undershoot amplitudes of the proposed LDO are obtained in 99.52/551.8 mV with the settling time of fewer than 1.3 μs for the load current changes from 0.1 to 100 mA with 200 ns rise/fall times.

Similar content being viewed by others

References

Lee, Y.-H., Yang, Y.-Y., Wang, S.-J., Chen, K.-H., Lin, Y.-H., Chen, Y.-K., et al. (2011). Interleaving energy-conservation mode (IECM) control in single-inductor dual-output (SIDO) step-down converters with 91% peak efficiency. IEEE Journal of Solid-State Circuits,46(4), 904–915.

Chen, Y., Kang, Y., Nie, S., & Pei, X. (2011). The multiple-output DC–DC converter with shared ZCS lagging leg. IEEE Transactions on Power Electronics,26(8), 2278–2294.

Carvajal, R., Ramirez-Angulo, J., Lopez-Martin, A., Torralba, A., Galan, J., Carlosena, A., et al. (2005). The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Transactions on Circuits and Systems I: Regular Papers,52(7), 1276–1291.

Saberkari, A., Alarcón, E., & Shokouhi, S. B. (2013). Fast transient current-steering CMOS LDO regulator based on current feedback amplifier. Integration,46(2), 165–171.

Cong, P., Chaimanonart, N., Ko, W. H., & Young, D. J. (2009). A wireless and batteryless 10-bit implantable blood pressure sensing microsystem with adaptive RF powering for real-time laboratory mice monitoring. IEEE Journal of Solid-State Circuits,44(12), 3631–3644.

Ho, M., Leung, K. N., & Mak, K.-L. (2010). A low-power fast-transient 90-nm low-dropout regulator with multiple small-gain stages. IEEE Journal of Solid-State Circuits,45, 2466–2475.

Wong, L., Hossain, S., Ta, A., Edvinsson, J., Rivas, D., & Naas, H. (2004). A very low-power CMOS mixed-signal IC for implantable pacemaker applications. IEEE Journal of Solid-State Circuits,39(12), 2446–2456.

Nasrollahpour, M., Hamedi-Hagh, S., Bastan, Y., & Amiri, P. (2017). ECP technique based capacitor-less LDO with high PSRR at low frequencies, − 89 dB PSRR at 1 MHz and enhanced transient response. In 2017 14th international conference on synthesis, modeling, analysis and simulation methods and applications to circuit design (SMACD).

Or, P. Y., & Leung, K. N. (2010). A fast-transient low-dropout regulator with load-tracking impedance adjustment and loop-gain boosting technique. IEEE Transactions on Circuits and Systems II: Express Briefs,57(10), 757–761.

Fathipour, R., Saberkari, A., Martinez, H., & Alarcón, E. (2014). High slew rate current mode transconductance error amplifier for low quiescent current output-capacitorless CMOS LDO regulator. Integration,47(2), 204–212.

Man, T. Y., Mok, P. K. T., & Chan, M. (2007). A high slew-rate push-pull output amplifier for low-quiescent current low-dropout regulators with transient-response improvement. IEEE Transactions on Circuits and Systems II: Express Briefs,54(9), 755–759.

El-Nozahi, M., Amer, A., Torres, J., Entesari, K., & Sanchez-Sinencio, E. (2010). High PSR low drop-out regulator with feed-forward ripple cancellation technique. IEEE Journal of Solid-State Circuits,45(3), 565–577.

Serdijn, W. A., Woerd, A. C., Roermund, A. H. M., & Davidse, J. (1995). Design principles for low-voltage low-power analog integrated circuits. Low-Voltage Low-Power Analog Integrated Circuits,8, 115–120.

Man, T. Y., Leung, K. N., Leung, C. Y., Mok, P., & Chan, M. (2008). Development of single-transistor-control LDO based on flipped voltage follower for SoC. IEEE Transactions on Circuits and Systems I: Regular Papers,55(5), 1392–1401.

Blakiewicz, G. (2011). Output-capacitorless low-dropout regulator using a cascoded flipped voltage follower. IET Circuits, Devices and Systems,5(5), 418.

Ho, M., & Leung, K. N. (2011). Dynamic bias-current boosting technique for ultralow-power low-dropout regulator in biomedical applications. IEEE Transactions on Circuits and Systems II: Express Briefs,58(3), 174–178.

Ramirez-Angulo, J., Gupta, S., Padilla, I., Carvajal, R., Torralba, A., Jimenez, M., & Munoz, F. (2005). Comparison of conventional and new flipped voltage structures with increased input/output signal swing and current sourcing/sinking capabilities. In 48th midwest symposium on circuits and systems.

Bastan, Y., Janipoor-Deylamani, M., & Amiri, P. (2018). Fast-transient capacitor-less low-dropout regulator with input current-differencing and dynamic current-boosting. Analog Integrated Circuits and Signal Processing. https://doi.org/10.1007/s10470-018-1289-z.

Elwan, H., Gao, W., Sadkowski, R., & Ismail, M. (2000). CMOS low-voltage class-AB operational transconductance amplifier. Electronics Letters,36(17), 1439.

Banker, G. P., & Naik, A. P. (2011). Comparative analysis of low power CMOS class—A voltage followers with current mirror as a load. IJECT,2(2), 108–111.

Bastan, Y., Hamzehil, E., & Amiri, P. (2016). Output impedance improvement of a low voltage low power current mirror based on body driven technique. Microelectronics Journal,56, 163–170.

Abdi, F., Deylamani, M. J., & Amiri, P. (2017). Slew rate and transient response enhancement in MOLDO with modifying error amplifier structure. Journal of Circuits, Systems and Computers,26(12), 1750197.

Lim, C.-C., Lai, N.-S., Tan, G.-H., & Ramiah, H. (2015). A low-power fast transient output capacitor-free adaptively biased LDO based on slew rate enhancement for SoC applications. Microelectronics Journal,46(8), 740–749.

Ho, M., Guo, J., Mak, K. H., Goh, W. L., Bu, S., Zheng, Y., et al. (2016). A CMOS low-dropout regulator with dominant-pole substitution. IEEE Transactions on Power Electronics,31(9), 6362–6371.

Li, C., & Chan, P. K. (2017). FVF LDO regulator with dual dynamic-load composite gain stage. Analog Integrated Circuits and Signal Processing,92(1), 131–140.

Perez-Bailon, J., Marquez, A., Calvo, B., & Medrano, N. (2017). An all-MOS low-power fast-transient 1.2 V LDO regulator. In 2017 13th conference on Ph.D. research in microelectronics and electronics (PRIME).

Yosef-Hay, Y., Larsen, D. Ø., Muntal, P. L., & Jørgensen, I. H. H. (2017). Fully integrated, low drop-out linear voltage regulator in 180 nm CMOS. Analog Integrated Circuits and Signal Processing,92(3), 427–436.

Joo, S., & Kim, S. (2018). Output-capacitor-free LDO design methodologies for high EMI immunity. IEEE Transactions on Electromagnetic Compatibility,60(2), 497–506.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Abdi, F., Bastan, Y. & Amiri, P. Dynamic current-boosting based FVF for output-capacitor-less LDO regulator. Analog Integr Circ Sig Process 101, 555–564 (2019). https://doi.org/10.1007/s10470-019-01479-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01479-x