Abstract

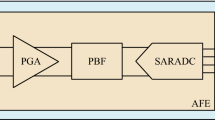

This paper presents an impact and low power algorithmic ADC which is implemented on a large scale field programmable analog array chip. The proposed circuit is merely composed of the elements within a single computational analog block (CAB) to minimize the area and parasitic effects. The feedback residue is amplified by a simple operational transconductance amplifier with a gain of \(-\,2\). Therefore, a new algorithm for the conversion process is proposed for this negative gain structure. Furthermore, owing to the floating-gate technique adopted in this work, the parameters and routes of the ADC achieve exceptional reconfigurability. The offset, reset, reference, threshold voltages, and gain all can be adjusted for optimizing the ADC performance. The measured results of the DNL is + 2/− 1 LSB and the INL is + 1.8/− 1.4 LSB, respectively. Under an 8-bit resolution and a 62.5 Hz sampling frequency condition, the measured effective number of bit is 7.6 bits. The total current consumption of the OTAs and FGOTAs is \(1.6\,\upmu\)A under a 2.5 V supply voltage. Each CAB which includes all components, switches, and routings occupies an area of \(400 \times 500\,{\mathrm{mm}}^2\).

Similar content being viewed by others

References

Nairn, D. G., & Salama, C. A. T. (1990). Current-mode algorithmic analog-to-digital converters. IEEE Journal of Solid-State Circuits, 25(4), 997–1004.

Jarvinen, J. A. M., Saukoski, M., & Halonen, K. A. I. (2008). A 12-bit ratio-independent algorithmic A/D converter for a capacitive sensor interface. IEEE Transactions on Circuits and Systems I: Regular Papers, 55(3), 730–740.

Li, P.-W., Chin, M., Gray, P., & Castello, R. (1984). A ratio-independent algorithmic analog-to-digital conversion technique. IEEE Journal of Solid-State Circuits, 19(6), 828–836.

Lu, C.-C. (2011). A 1.5V IO-bit 5 MS/s CMOS algorithmic ADC. International Congress on Image and Signal Processing (CISP), 4(1), 2146–2149.

George, S., Kim, S., Shah, S., Hasler, J., Collins, M., Adil, F., et al. (2016). A programmable and configurable mixed-mode FPAA SoC. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 24(6), 2253–2261.

Peng, S. -Y., Gurun, G., Twigg, C. M., Qureshi, M. S., Basu, A., Brink, S., Hasler, P. E., & Degertekin F. L. (2009). A large-scale reconfigurable smart sensory chip. In IEEE international symposium on circuits and systems (pp. 2145–2148).

Ma, Y., Gilliland, T. G., Wang, B., Paulsen, R., Pesavento, A., Wang, C.-H., et al. (2004). Reliability of PFET EEPROM with 70-åtunnel oxide manufactured in generic logic CMOS processes. IEEE Transactions on Device and Materials Reliability, 4(3), 353–358.

Monk, T. A., Hurst, P. J., & Lewis, S. H. (2016). Iterative gain enhancement in an algorithmic ADC. IEEE Transactions on Circuits and Systems I: Regular Papers, 63(3), 459–469.

Peng, S.-Y., Qureshi, M. S., Hasler, P. E., Basu, A., & Degertekin, F. L. (2008). A charge-based low-power high-SNR capacitive sensing interface circuit. IEEE Transactions on Circuits and Systems I: Regular Papers, 55(7), 1863–1872.

Geelen, G. (2001). A 6 b 1.1 GSample/s CMOS A/D converter. In IEEE international solid-state circuits conference (pp. 128–129).

Erdogan, O. E., Hurst, P. J., & Lewis, S. H. (1999). A 12-b digital-background-calibrated algorithmic ADC with -90-dB THD. IEEE Journal of Solid-State Circuits, 34(12), 1812–1820.

Kim, M. G., Hanumolu, P. K., & Moon, U.-K. (2009). A 10 MS/s 11-bit 0.19 \({\rm mm}^2\) algorithmic ADC with improved clocking scheme. IEEE Journal of Solid-State Circuits, 44(9), 2348–2355.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wang, TY., Peng, SY. & Hasler, J. A compact low-power algorithmic A/D converter implemented on a large scale FPAA chip. Analog Integr Circ Sig Process 94, 65–74 (2018). https://doi.org/10.1007/s10470-017-1084-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-017-1084-2