Abstract

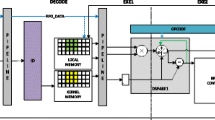

There is an increasing demand for high performance image processing platforms based on field programmable gate array (FPGA). The Histogram of Orientated Gradients (HOG) algorithm is a feature descriptor algorithm used in object detection for many security applications. The chapter examines the implementation of this key algorithm using an FPGA-based soft-core architecture approach. Firstly, the HOG algorithm is described and its performance profiled from a computation and bandwidth perspective. Then the IPPro soft-core processor architecture is introduced and a number of map** strategies are covered. A HOG implementation is demonstrated on a Zynq platform, resulting in a design operating at 15.36 fps; this compares favorably with the performance and resources of hand-crafted VHDL code.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Woods R, McAllister J, Lightbody G and Yi Y (2017) FPGA-based Implementation of Signal Processing Systems. 2nd edn. Wiley, UK.

Jain R, Kasturi R and Schunck B G (1995) Machine Vision. McGraw-Hill, Inc.

Deschamps J P, Sutter G D and Cantó E. (2012) Guide to FPGA Implementation of Arithmetic Functions. Springer.

**linx Inc. (2016) System Generator for DSP. Available via http://www.xilinx.com. Cited 29 April 2017.

MathWorks (2016) HDL Coder. Available via http://uk.mathworks.com/products/hdl-coder/index.html. Cited 29 April 2017.

McKinsey and Company (2012) McKinsey on Semiconductors. Available via http://www.mckinsey.com. Cited 29 April 2017.

**linx Inc. (2015) DS183: Viretx-7 and XT FPGAs Data Sheet: DC and AC Switching Characteristics. Available via http://www.xilinx.com. Cited 29 April 2017.

ARM Ltd. ARM7TDMI Technical Reference Manual (ARM DDI 0029G). Available via http://www.atmel.com. Cited 29 April 2017.

**linx Inc. (2011) LogiCORE IP Divider Generator v3.0. Available via http://www.xilinx.com. Cited 29 April 2017.

Texas Instruments (2010) TMS3206678 Rev.E. Available via http://www.ti.com. Cited 29 April 2017.

Eker J and Janneck J (2003) CAL language report. University of California at Berkeley Technical Report UCB/ERL M, (3).

Blair C, Robertson N M and Hume D (2013) Characterizing a Heterogeneous System for Person Detection in Video Using Histograms of Oriented Gradients: Power Versus Speed Versus Accuracy. IEEE Journal on Emerging and Selected Topics in Circuits and Systems. 3(2), 1236–247.

Oberman S F and Flynn M (1997) Division algorithms and implementations. IEEE Transactions on Computers, 46(8), 833–854.

Robertson J E (1958) A New Class of Digital Division Methods. IRE Transactions on Electronic Computers, EC-7(3), 218–222.

Macii E, Paliouras V and Koufopavlou O (2004) Power Aware Dividers in FPGA. Proc. of Power and Timing Modeling, Optimization and Simulation, 574–584.

Thomas D B, Howes L and Luk W (2009) A Comparison of CPUs, GPUs, FPGAs, and Massively Parallel Processor Arrays for Random Number Generation. Proc. of ACM/SIGDA International Symposium on Field Programmable Gate Arrays, 63–72.

Dalal N and Triggs B (2005) Histograms of oriented gradients for human detection. Proc. of IEEE Conference on Computer Vision and Pattern Recognition, 886–893.

Hahnle M, Saxen F, Hisung M, Brunsmann U and Doll K (2013) FPGA-Based Real-Time Pedestrian Detection on High-Resolution Images. Proc. of IEEE Conference on Computer Vision and Pattern Recognition, 629–635.

Bauer S, Brunsmann U and Schlotterbeck-Macht S (2009) FPGA Implementation of a HOG-based Pedestrian Recognition System. Proc. of IMPC-Workshop, Karlsruhe.

**e S, Li Y, Jia Z and Ju L (2013) Binarization based implementation for real-time human detection. Proc. of International Conference on Field-Programmable Technology, 1–4.

Kadota R, Sugano H, Hiromoto M, Ochi H, Miyamoto R and Nakamura Y (2009) Hardware Architecture for HOG Feature Extraction. Proc. of International Conference on Intelligent Information Hiding and Multimedia Signal Processing, 1330–1333.

Siddiqui F M, Russell M, Bardak B, Woods R and Rafferty K (2014) IPPro: FPGA based image processing processor. Proc. of IEEE Workshop on Signal Processing Systems, 1–6.

Kelly C, Siddiqui F M, Bardak B and Woods R (2014) Histogram of oriented gradients front end processing: an FPGA based processor approach. Proc. of IEEE Workshop on Signal Processing Systems, 1–6.

Negi K, Dohi K, Shibata Y and Oguri K (2011) Deep pipelined one-chip FPGA implementation of a real-time image-based human detection algorithm. Proc. of International Conference on Field-Programmable Technology, 1–8.

Acknowledgements

This work has been undertaken in collaboration with Heriot-Watt University in a project funded by the Engineering and Physical Science Research Council (EPSRC) through the EP/K009583/1 grant. Colm Kelly has received support from Thales Air Defence.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer International Publishing AG, part of Springer Nature

About this chapter

Cite this chapter

Kelly, C., Woods, R., Amiri, M., Siddiqui, F., Rafferty, K. (2019). Programmable Architectures for Histogram of Oriented Gradients Processing. In: Bhattacharyya, S., Deprettere, E., Leupers, R., Takala, J. (eds) Handbook of Signal Processing Systems. Springer, Cham. https://doi.org/10.1007/978-3-319-91734-4_18

Download citation

DOI: https://doi.org/10.1007/978-3-319-91734-4_18

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-91733-7

Online ISBN: 978-3-319-91734-4

eBook Packages: EngineeringEngineering (R0)