Abstract

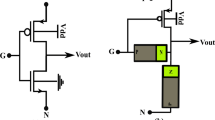

This paper presents ternary unary operators and multiplexer circuits in carbon nanotube field effect transistor and memristor technology. The designed circuits can be used in designing ternary arithmetic circuits, a ternary full adder is proposed in this paper using ternary unary operators and multiplexers. The proposed circuits are simulated in Cadence Virtuoso using MOSFET-like CNFET and VTEAM memristor model. The proposed ternary full adder is having a savings of 17\(\%\) in the power delay product to the best existing designs. Noise margin analysis was carried out on the proposed circuits and proposed ternary full adder is having a good noise margin.

This work has been supported by the DST, Start up Research Grant - SRG/2021/001255.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Smith, K.C.: The prospects for multivalued logic: a technology and applications view. IEEE Trans. Comput. C–30(9), 619–634 (1981)

Raychowdhury, A., Roy, K.: Carbon-nanotube-based voltage-mode multiple-valued logic design. IEEE Trans. Nanotechnol. 4(2), 168–179 (2005)

Lin, S., Kim, Y.-B., Lombardi, F.: Design of a ternary memory cell using CNTFETs. IEEE Trans. Nanotechnol. 11(5), 1019–1025 (2012)

Lin, S., Kim, Y.-B., Lombardi, F.: CNTFET-based design of ternary logic gates and arithmetic circuits. IEEE Trans. Nanotechnol. 10(2), 217–225 (2011)

Srinivasu, B., Sridharan, K.: Low-complexity multiternary digit multiplier design in CNTFET technology. IEEE Trans. Circuits Syst. II Express Briefs 63(8), 753–757 (2016)

Hurst, S.L.: Multiple-valued logic? Its status and its future. IEEE Trans. Comput. 33(12), 1160–1179 (1984)

Karmakar, S., Jain, F.C.: Ternary static random access memory using quantum dot gate field-effect transistor. Micro Nano Lett. 10(11), 621–624 (2015)

Kvatinsky, S., Ramadan, M., Friedman, E.G., Kolodny, A.: VTEAM: a general model for voltage-controlled memristors. IEEE Trans. Circuits Syst. II Express Briefs 62(8), 786–790 (2015)

Zangeneh, M., Joshi, A.: Design and optimization of nonvolatile multibit 1T1R resistive RAM. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 22(8), 1815–1828 (2013)

Kvatinsky, S., Belousov, D., et al.: MAGIC-memristor-aided logic. IEEE Trans. Circuits Syst. II Express Briefs 61(11), 895–899 (2014)

Kvatinsky, S., Satat, G., et al.: Memristor-based material implication (IMPLY) logic: design principles and methodologies. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 22(10), 2054–2066 (2013)

Wang, X.-Y., et al.: High-density memristor-CMOS ternary logic family. IEEE Trans. Circuits Syst. I Regul. Pap. 68(1), 264–274 (2020)

Mohammed, M.U., Vijjapuram, R., Chowdhury, M.H.: Novel CNTFET and memristor based unbalanced ternary logic gate. In: 2018 IEEE 61st International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 1106–1109 (2018)

Miller, D.M., Thornton, M.A.: Multiple valued logic: concepts and representations. Synth. Lect. Digit. Circuits Syst. 2(1), 1–127 (2007)

Srinivasu, B., Sridharan, K.: A synthesis methodology for ternary logic circuits in emerging device technologies. IEEE Trans. Circuits Syst. I Regul. Pap. 64(8), 2146–2159 (2017)

Vudadha, C., Surya, A., Agrawal, S., Srinivas, M.: Synthesis of ternary logic circuits using 2: 1 multiplexers. IEEE Trans. Circuits Syst. I Regul. Pap. 65(12), 4313–4325 (2018)

Zahoor, F., Zulkifli, T.Z.A., Khanday, F.A., Zainol Murad, S.A.: Carbon nanotube and resistive random access memory based unbalanced ternary logic gates and basic arithmetic circuits. IEEE Access 8, 104 701–104 717 (2020)

Stanford University CNTFET model. Stanford University, Stanford, CA (2008). http://nano.stanford.edu/model_stan_cnt.htm

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Srikanth, P., Srinivasu, B. (2022). High Performance Ternary Full Adder in CNFET-Memristor Logic Technology. In: Shah, A.P., Dasgupta, S., Darji, A., Tudu, J. (eds) VLSI Design and Test. VDAT 2022. Communications in Computer and Information Science, vol 1687. Springer, Cham. https://doi.org/10.1007/978-3-031-21514-8_35

Download citation

DOI: https://doi.org/10.1007/978-3-031-21514-8_35

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-21513-1

Online ISBN: 978-3-031-21514-8

eBook Packages: Computer ScienceComputer Science (R0)