Abstract

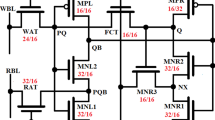

The design solution described in Chap. 5 will help the minimum operating voltage (VDDmin) of a general 6T single-port SRAM. However, it will eventually face the limitation of the SRAM VDDmin because of the degradation of the SRAM stability due to an increase in the local V th variation. In this chapter, first some alternative 6T single-port SRAM cells to enhance the SRAM stability are introduced in Sect. 7.1.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

K. Takeda, Y. Hagihara, Y. Aimoto, M. Nomura, Y. Nakazawa, T. Ishii, H. Kobatake, A read-static-noise-margin-free SRAM cell for low-VDD and high-speed applications. IEEE J. Solid-State Circuits 41(1), 113–121 (2006)

Y. Morita, H. Fujiwara, H. Noguchi, Y. Iguchi, K. Nii, H. Kawaguchi, M. Yoshimoto, An area-conscious low-voltage-oriented 8T-SRAM design under DVS environment. in IEEE VLSI Circuits Symposium Digest. June 2007, pp. 256–257

H. Noguchi, Y. Iguchi, H. Fujiwara, Y. Morita, K. Nii, H. Kawaguchi, M. Yoshimoto, A 10T non-precharge two-port SRAM for 74% power reduction in video processing. in Proceedings of the IEEE Computer Society Annual Symposium VLSI (ISVLSI). March 2007, pp. 107–112

B. Cheng, S. Roy, A. Asenov, The scalability of 8T-SRAM cells under the influence of intrinsic parameter fluctuations. in Proceedings of the IEEE European Solid-State Circuits Conference (ESSCIRC). September 2007, pp. 93–96

Y. Morita, H. Fujiwara, H. Noguchi, Y. Iguchi, K. Nii, H. Kawaguchi, M. Yoshimoto, Area comparison between 6T and 8T SRAM cells in dual-Vdd scheme and DVS scheme. IEICE Trans. Fundam. E90-A(12), 2695–2702 (2007)

Y. Morita, R. Tsuchiya, T. Ishigaki, N. Sugii, T. Iwamatsu, T. Ipposhi, H. Oda, Y. Inoue, K. Torii, S. Kimura, Smallest Vth variability achieved by intrinsic silicon on thin BOX (SOTB) CMOS with single metal gate. in IEEE VLSI Technology Symposium 2008, Digest of Technical Papers. June 2008, pp. 166–167

K. Noda, K. Matsui, K. Imai, K. Inoue, K. Tokashiki, H. Kawamoto, K. Yoshida, K. Takeda, N. Nakamura, T. Kimura, H. Toyoshima, Y. Koishikawa, S. Maruyama, T. Saitoh, T. Tanigawa, A 1. 9 − μm2 loadless CMOS four-transistor SRAM cell in a 0. 18 − μm logic technology. inIEEE IEDM Technical Digest. December 1998, pp. 643–646

D. Hisamoto, W.-C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T.-J. King, J. Bokor, C. Hu, FinFET–A self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 47, 2320–2325 (2000)

A. Nackaerts, M. Ercken, S. Demuynck, A. Lauwers, C. Baerts, H. Bender, W. Boulaert, N. Collaert, B. Degroote, C. Delvaux, J.F. de Marneffe, A. Dixit, K. De Meyer, E. Hendrickx, N. Heylen, P. Jaenen, D. Laidler, S. Locorotondo, M. Maenhoudt, M. Moelants, I. Pollentier, K. Ronse, R. Rooyackers, J. Van Aelst, G. Vandenberghe, W. Vandervorst, T. Vandeweyer, S. Vanhaelemeersch, M. Van Hove, J. Van Olmen, S. Verhaegen, J. Versluijs, C. Vrancken, V. Wiaux, M. Jurczak, S. Biesemans, A 0. 314μm2 6T-SRAM cell build with tall triple-gate devices for 45nm node applications using 0.75NA 193nm lithography. IEDM Tech. Dig. 269–272 (2004)

H. Kawasaki, K. Okano, A. Kaneko, A. Yagishita, T. Izumida, T. Kanemura, K. Kasai, T. Ishida, T. Sasaki, Y. Takeyama, N. Aoki, N. Ohtsuka, K. Suguro, K. Eguchi, Y. Tsunashima, S. Inaba, K. Ishimaru, H. Ishiuchi, Embedded bulk FinFET SRAM cell technology with planar FET peripheral circuit for hp32 nm node and beyond. in VLSI Technology, Digest of Technical Papers. 2006 Symposium on 2006, pp. 70–71

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2011 Springer-Verlag Berlin Heidelberg

About this chapter

Cite this chapter

Nii, K., Yamaoka, M. (2011). Future Technologies. In: Ishibashi, K., Osada, K. (eds) Low Power and Reliable SRAM Memory Cell and Array Design. Springer Series in Advanced Microelectronics, vol 31. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-19568-6_7

Download citation

DOI: https://doi.org/10.1007/978-3-642-19568-6_7

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-19567-9

Online ISBN: 978-3-642-19568-6

eBook Packages: EngineeringEngineering (R0)