Abstract

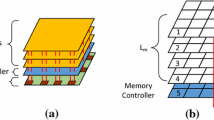

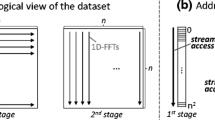

FPGA-based systems consisting external memory have been extensively employed in data intensive applications such as signal, image, and network processing. Memory energy is a dominating factor in the overall system energy dissipation. In particular, when performing non-sequential memory access patterns, significant amount of energy is dissipated due to frequent memory row activations. In this paper, we consider the classic stride memory access pattern and evaluate the energy consumption in DRAM. Lower bounds on DRAM energy consumption are derived for this widely used memory access pattern which introduces row-wise writing and column-wise reading memory operations. To achieve the lower bounds of the DRAM energy consumption, we remap data onto DRAM for both row-wise and column-wise memory operations. This significantly reduces the latency brought by frequent DRAM row activations due to column-wise memory operations. We validate experimentally our analysis using 2-D FFT as a benchmark application on FPGA-based system. The experimental results demonstrate that our proposed optimizations result in 74.8 %\(\sim \)77.7 % reduction in energy consumption of the overall system compared with the baseline for 1024\(\times \) 1024, 4096\(\times \) 4096, and 8192\(\times \) 8192 points 2-D FFTs, respectively.

This work was supported by the DARPA under grant HR0011-12-2-0023, and the U.S. National Science Foundation under grants CCF-1320211 and ACI-1339756. Equipment grant from **linx, Inc. is gratefully acknowledged.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

DDR3 SDRAM System-Power Calculator. http://www.micron.com/-/media/Documents/Products/Power%20Calculator/DDR3_Power_Calc.XLSM

Micron DRAM. http://www.micron.com/products/dram/

Vivado design suite user guide: design flows overview. http://www.xilinx.com/support/documentation/

**linx Zynq board. http://www.xilinx.com/products/silicon-devices/soc/zynq-7000.html

Akin, B., Milder, P., Franchetti, F., Hoe, J.: Memory bandwidth efficient two-dimensional fast fourier transform algorithm and implementation for large problem sizes. In: Proc. of IEEE FCCM 2012, pp. 188–191, April 2012

Chen, R., Le, H., Prasanna, V.K.: Energy efficient parameterized FFT architecture (2013)

Chen, R., Park, N., Prasanna, V.K.: High throughput energy efficient parallel FFT architecture on FPGAs. In: Proc. of IEEE Intl. Con. on HPEC (2013)

Chen, R., Prasanna, V.: Energy and memory efficient map** of bitonic sorting on fpga. In: Proc. of ACM/SIGDA International Symposium on FPGA (2015)

Fang, K., Zhu, Z.: Conservative row activation to improve memory power efficiency. In: Proc. of ACM ICS 2013, pp. 81–90. ACM, New York (2013)

Park, N., Hong, B., Prasanna, V.: Tiling, block data layout, and memory hierarchy performance. IEEE Transactions on Parallel and Distributed Systems 14(7), 640–654 (2003)

Rixner, S., Dally, W.J., Kapasi, U.J., Mattson, P., Owens, J.D.: Memory Access Scheduling. SIGARCH Comput. Archit. News 28(2), 128–138 (2000)

Singh, M., Prasanna, V.K.: Algorithmic techniques for memory energy reduction. In: Jansen, K., Margraf, M., Mastrolli, M., Rolim, J.D.P. (eds.) WEA 2003. LNCS, vol. 2647, pp. 237–252. Springer, Heidelberg (2003)

Son, Y.H., Seongil, O., Ro, Y., Lee, J.W., Ahn, J.H.: Reducing memory access latency with asymmetric dram bank organizations. In: Proc. of ISCA 2013, pp. 380–391. ACM, New York (2013)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2015 Springer International Publishing Switzerland

About this paper

Cite this paper

Chen, R., Prasanna, V.K. (2015). DRAM Row Activation Energy Optimization for Stride Memory Access on FPGA-Based Systems. In: Sano, K., Soudris, D., Hübner, M., Diniz, P. (eds) Applied Reconfigurable Computing. ARC 2015. Lecture Notes in Computer Science(), vol 9040. Springer, Cham. https://doi.org/10.1007/978-3-319-16214-0_30

Download citation

DOI: https://doi.org/10.1007/978-3-319-16214-0_30

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-16213-3

Online ISBN: 978-3-319-16214-0

eBook Packages: Computer ScienceComputer Science (R0)