Abstract

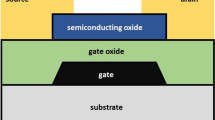

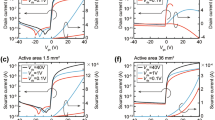

The metal-oxide-semiconductor field effect transistor, MOSFET, is the most widely studied and understood IGFET, and is used here to describe key aspects of IGFET behaviour. The topic is introduced by a physical description of MOSFET operation, which identifies the linear and saturation operating regimes. A simple analytical model is developed from this, yielding expressions for important parameters such as threshold voltage, saturation voltage and carrier mobility. These are extensively used in TFT analysis. A more rigorous analysis is presented to explicitly include the role of substrate do**, and its effect upon saturation voltage. These descriptions are valid for the on-state regime, in which the gate bias, VG, is greater than the threshold voltage, VT. A further operating regime is described for VG < VT, which is referred to as the sub-threshold regime. In this regime, the current increases exponentially with gate bias, and is characterised by the sub-threshold slope. This is another concept, and parameter, which is widely used in the analysis of TFT behaviour. Finally, the role of film thickness, in thin film devices, in modifying the standard expressions for threshold voltage and saturation voltage is presented.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Grove AS (1967) Physics and technology of semiconductor devices. John Wiley and Sons Inc, New York

Grove AS, Fitzgerald DJ (1966) Surface effects on p-n junctions: characteristics of surface space-charge regions under non-equilibrium conditions. Solid-State Electron 9:783–806

Brews JR (1979) Subthreshold behaviour of uniformly and nonuniformly doped long-channel MOSFET. IEEE Trans ED-26 9:1282–1291

Taylor GW (1978) Subthreshold conduction in MOSFETs. IEEE Trans ED-25 3:337–380

Powell MJ (1989) The physics of amorphous-silicon thin-film transistors. IEEE Trans ED-36(12):2753–2763

Bonfiglietti A, Valletta A, Gaucci P, Mariucci L, Fortunato G, Brotherton SD (2005) Electrical characterisation of directionally solidified polycrystalline silicon. J Appl Phys 98(3):033702

Klauk H, Zschieschang U, Pflaum J, Halik M (2007) Ultralow-power organic complementary circuits. Nature 445:745–748

Nomura K, Takagi A, Kamiya T, Ohta H, Hirano M, Hosono H (2006) Amorphous oxide semiconductors for high-performance flexible thin-film transistors. Jpn J Appl Phys 45(5B):4303–4308

Shannon JM, Balon F (2007) High-performance thin-film transistors in disordered and poor-quality semiconductors. IEEE Trans ED-54(2):354–358

Author information

Authors and Affiliations

Appendix: Summary of Key Equations

Appendix: Summary of Key Equations

A number of the simplified equations from the text, which can be used in basic analytical calculations, are reproduced below. The equation numbers are retained for quick reference back to the original derivations.

1.1 Simplified MOSFET On-State Analysis

Relationships between the drain current, and the gate and drain biases.

(a) drain current as a function of terminal biases

(b) threshold voltage

(c) linear regime current

(d) linear regime mobility

(e) linear regime transconductance

(f) saturation regime current

(g) saturation regime mobility

(h) saturation regime transconductance

1.2 Simplified MOSFET Sub-Threshold Analysis

(a) sub-threshold current

(b) relationship between surface potential, Vs, and gate bias

(c) sub-threshold slope, S

(d) sub-threshold slope with interface states

(e) interface state capacitance

Rights and permissions

Copyright information

© 2013 Springer International Publishing

About this chapter

Cite this chapter

Brotherton, S.D. (2013). Insulated Gate Field Effect Transistors, IGFETs. In: Introduction to Thin Film Transistors. Springer, Heidelberg. https://doi.org/10.1007/978-3-319-00002-2_3

Download citation

DOI: https://doi.org/10.1007/978-3-319-00002-2_3

Published:

Publisher Name: Springer, Heidelberg

Print ISBN: 978-3-319-00001-5

Online ISBN: 978-3-319-00002-2

eBook Packages: Physics and AstronomyPhysics and Astronomy (R0)