Abstract

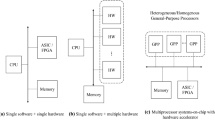

In traditional design methodologies, the system designer typically develops the application in a sequential paradigm almost to completion before addressing issues of parallelism and map** to a heterogeneous architecture. As the architectural complexity of these applications increase, however, this process becomes too costly since implementation must be started anew after the design. The quality of the design also often suffers as a result. This is especially true for embedded applications, where the complexity lies within the system software and hardware architecture. We present a new methodology and toolset aimed at improving the system development process for high-performance embedded applications. The toolset provides a unified design representation from early design specification to integration—allowing for parallelism and synchronization specification in domain specific styles, and automating many process steps such as partitioning/map**, simulation, glue-code generation, and performance analysis.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Devesh Bhatt, Vicraj Thomas, and John Shackleton, “A Methodology and Toolset for the Design of Parallel Embedded Systems,” ACM OOPS Messenger, January 1996.

Peter Coad and Edward Yourdon, Object-Oriented Analysis, Second Edition, Yourdon Press, Prentice Hall Building.

S. Shlaer, S. J. Miller, “Object Lifecycles: Modeling the World in States,” Yourdon Press, Prentice Hall Building, 1992.

J. Rumbaugh, M. Blaha, W. Premerlani, F. Eddy, and W. Loresnsen, Object-Oriented Modeling and Design, Prentice Hall, Englewodd Cliffs, NJ 07632.

David Grimm and John Samson, “Data Flow Shell Environment for Deterministic Signal Processing Applications,” Technical Report, Space Systems Division, Honeywell, Inc., April 1995.

D. Cottel and P. Partow, “Experience Building a Scalable Programming Environment,” Intel Supercomputer Users Group Conference (ISUG-94), June 1994.

J. T. Buck, S. Ha, E. A. Lee, and D. G. Messerschmitt, “Ptolemy: A Framework for Simulating and Prototy** Heterogeneous Systems,” Int. Journal of Computer Simulation, special issue on “Simulation Software Development,” vol. 4, pp. 155–182, April 1994.

Gul Agha, Svend Frolund, WooYoung Kim, Rajendra Panwar, Anna Patterson, and Daniel Sturman, “Abstractions and Modularity Mechanisms for Concurrent Computing,” IEEE Parallel and Distributed Technology, vol. 1, no. 2, May 1993.

D. Cottel and P. Partow, “Scalable Programming Environment”. Technical Report 1672 Rev. 1, September 1995.

A. Kalavade and E. A. Lee, “The Extended Partitioning Problem: Hardware/Software Map** and Implementation-Bin Selection,” Journal of Design Automation for Embedded Systems, March 1997.

K. Mani Chandy, Rajit Manohar, Berna L. Massingill, Daniel I. Meiron, “Integrating Task and Data Parallelism with the Group Communication Archetype”, Proceedings of the 9th International Parallel Processing Symposium, April 1995.

Fred Rose, John Shackleton, and Carl Hein, “Performance Modeling of System Architectures,” Journal of VLSI Signal Processing 15, 97–109, 1997.

Devesh Bhatt, Rashmi Bhatt, Rakesh Jha, Todd Steeves, and David Wills, “SPI: an Instrumentation Development Environment for Parallel/Distributed Systems,” Proceedings of the 9th International Parallel Processing Symposium, April 1995.

Author information

Authors and Affiliations

Editor information

Rights and permissions

Copyright information

© 1998 Springer-Verlag Berlin Heidelberg

About this chapter

Cite this chapter

Bhatt, D., Shackleton, J. (1998). A design notation and toolset for high-performance embedded systems development. In: Rozenberg, G., Vaandrager, F.W. (eds) Lectures on Embedded Systems. EEF School 1996. Lecture Notes in Computer Science, vol 1494. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-65193-4_24

Download citation

DOI: https://doi.org/10.1007/3-540-65193-4_24

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-65193-2

Online ISBN: 978-3-540-49498-0

eBook Packages: Springer Book Archive