Abstract

In this paper, we propose the use of punch-through nMOS (PTnMOS) as an alternative to pMOS in complementary metal oxide semiconductor (CMOS) circuits. According to the TCAD simulation results, PTnMOS exhibit sub-threshold characteristics similar to those of pMOS and can be formed by simply changing the do** concentration of the source and drain. Without the need for sizing, which solves the area occupation problem caused by the need to increase the width of pMOS due to insufficient hole mobility. In addition, we compose a PTnMOS and nMOS without sizing to form a single-carrier CMOS in which only electrons are transmitted, and We extract its performance for comparison with conventional CMOS (Wp/Wn = 1). The results indicate that single-carrier CMOS has symmetric noise margin and 29% faster delay time compared to conventional CMOS (Wp/Wn = 1). If III–V or II–VI group materials could be applied to single-carrier CMOS, not only could costs be reduced and wafer area occupancy minimized, but also significant improvements in the performance and bandwidth application of microwave circuits could be achieved.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Complementary metal oxide semiconductor circuits were first proposed by Wanlass and Sah in 1963 [1] and are widely used in the modern semiconductor industry because of their extremely low static power dissipation and symmetrical noise margin. However, the mismatch of carrier mobility has always been a problem in conventional CMOS circuits. In conventional CMOS circuits, electrons and holes are the carriers of nMOS and pMOS respectively. The performance of conventional CMOS circuits is degraded since the electrons move faster than the holes, so it is necessary to make the width of the pMOS about three times wider than that of the nMOS to compensate for the problem of lower hole mobility [2], which increases both the cost of the process and the total area of layout.

Researchers have used various methods to address this. For instance, early research focused on studying different surface orientations and their effectiveness in enhancing pMOS performance [3,4,5]. In practice, there are limitations due to interface capture, which can compromise the reliability of the device [6]. Another method is to replace channel materials with high carrier mobility materials, such as Ge [7, 8]. However, performance degradation in ultra-thin body (UTB) Germanium on Insulator (GeOI) pMOS devices has been identified because of poor Ge/buried oxide (BOX) interfaces and GeOI thickness variations [9, 10]. Strained SOI (SSOI) has emerged as a promising option for sub-10 nm technology nodes when compared to bulk silicon and SOI technologies [11]. Strain technologies are classified as local process-induced technologies and include strained overlays [12], embedded source/drain stressors [13], stress memory technology (SMT) [14] or strained contacts and metal gates [15]. Despite the potential benefits of strain technology, its complexity can increase manufacturing costs and difficulties.

In this paper, we discuss the operating mechanism and electrical analysis of PTnMOS by TCAD simulation. Our previous studies [16, 17] have demonstrated the feasibility of the PTnMOS. However, to prevent PTnMOS from generating inversion current, it is necessary to use two embedded oxides, which significantly increases manufacturing costs and poor sub-threshold swing. Therefore, this paper proposes to use a planar fully depleted silicon-on-insulator (FD-SOI) structure to improve the control of punch-through current and inversion current switching. The planar FD-SOI structure offers better gate control, allowing it to operate at a lower supply voltage [18,19,20]. This enables the current to be turned off before the strong inversion occurs, so that it is not affected by the strong inversion current. Then, we present a comprehensive study and optimization of the PTnMOS is carried out. Finally, the application of single-carrier CMOS consisting of the proposed PTnMOS and nMOS in basic logic circuits is discussed.

2 Structure design and fabrication

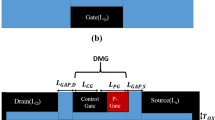

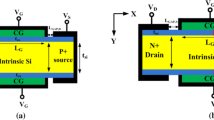

Figure 1 shows the structure of conventional CMOS circuit and our proposed single-carrier CMOS circuit, and the fabrication process of single carrier CMOS circuit. We chose channel length 22 nm because approximately 75% of the process steps are common to the 28 nm platform, improving yield capability. Firstly, in-situ doped boron 10 nm SOI and 145 nm oxygen embedded were used as initial substrates. Then shallow trench isolation (STI) is used to define the active region for PTnMOS and nMOS device. After patterning the gate structure, High-k gate dielectric (HfO2) is deposited by atomic layer deposition (ALD), followed by deposition of polysilicon gate. Then only lightly doped the source/drain of the nMOS. This is to avoid that lightly doped the source/drain of the PTnMOS will reduce the punch-through effect. After the formation of the SiO2 sidewall, phosphorus ion implantation and activation of the dopant by rapid thermal annealing (RTA) are performed on the source/drain of both nMOS and PTnMOS. Finally, the poly-Si gate is replaced with a metal gate (NiSi), followed by Middle of Line (MOL) and Back End of Line (BEOL) processes.

3 Physical mechanism and simulation method

Figure 2 shows a schematic diagram of the operation of the PTnMOS. According to Fu-Chieh Hsu et al. [21], when the device is operated in accumulation mode (gate bias (VG) is below the flat-band voltage (VFB)), punch-through occurs below the surface (i.e., the lowest barrier path seen by the electrons between the source and the drain is below the surface). The magnitude of the current is determined by the minimum potential value along this path, resulting in a punch-through current as shown in Fig. 2a. The black dotted lines in Fig. 2a represent the depleted region of the source/channel and the drain/channel, respectively. As a result, PTnMOS operate with a negative gate bias, providing electrical characteristics similar to those of pMOS. When the device is operated in weak inversion mode (gate bias is above the flat-band voltage but below the threshold voltage (Vth)), depleted region is formed between gate oxide and channel. As the gate bias increases, the depletion region between the gate and the channel expands. This results in the separation of the depletion region between the source/channel and the drain/channel, preventing the formation of a punch-through current and leading to a closed state, as shown in Fig. 2b. The green dotted line in Fig. 2b represents the depletion region between the gate oxide and the channel.

Table 1 shows the device parameters of our proposed PTnMOS, and device structure shown in Fig. 3. In order to match our proposed PTnMOS with the results of real fabrication measurements, we calibrated the 22 nm FD SOI presented by Carter et al. [22] at IEDM 2016 using Silvaco Athena [23] and Atlas [24]. Considering various carrier generation-recombination models, including SRH, CONSRH, and AUGER. Additionally, we considered the impact ionization model IMPACT SELB. The thinness of the gate insulation layer may cause potential gate leakage current issues. To consider this, models such as BBT.KL, FNORD, and FNHOLES were used. We also considered carrier mobility models such as CONMOB, FLDMOB, and CVT, as well as Fermi and BGN carrier statistics models. Figure 4 shows the results of calibrating the PTnMOS using the aforementioned model. It is evident that the model parameters we have employed closely resemble the actual situation.

4 Result and discussion

4.1 Effect of changing source/drain concentration on PTnMOS.

Figure 5 shows the ID–VG characteristics of PTnMOS with different source/drain concentrations at a fixed channel concentration. The gate workfunction is set at 4.65 eV (i.e. VFB = 0 V) while the source/drain concentration is adjusted to achieve punch-through. The results indicate that PTnMOS can be fabricated when the source/drain concentration is approximately 2 to 3 times higher than the channel concentration, and its electrical properties are similar to those of pMOS. From the source/drain concentration of 2 × 1017 cm−3, it can be found that when VG < VFB (negative gate bias), the depletion region between source/channel and drain/channel touch each other, resulting in a punch-through current that reaches the on-state. When VFB < VG < Vth (gate bias is positive), the depletion region of gate oxide/channel grows with increasing gate bias, pushing the depletion region of source/channel away from the depletion region of drain/channel to block the punch-through current and reach the off-state. Figure 6 shows the potential of PTnMOS to change the source/drain concentration at VG = − 1 V. It can be observed that the punch-through current is higher for the lower barrier paths when the PTnMOS is operated in the accumulation mode. This is consistent with what we mentioned in Section III, that the punch-through current is determined by the value of the minimum potential along the path. Figure 7 illustrates the output characteristics of PTnMOS. It can be observed that the punch-through current decreases when VG increases.

4.2 PTnMOS operating modes

Figure 8 shows the energy band diagram at different gate voltages. To observe the operating mode of the PTnMOS, we fixed the channel concentration at 1017 cm−3 and the source/drain concentration at 2 × 1017 cm−3. We observe the changes of the energy band diagrams along A to A′. Figure 8a shows that when VG = − 1 V, the energy band of the oxide and semiconductor interface is upward curved and the same as that of the nMOS operation in the accumulating mode. This indicates that the PTnMOS operation is turned on in the accumulating mode. Then we observe the energy band diagram at VG = 1 V as shown in Fig. 8b, the energy band of the oxide and semiconductor interface is downward curved, which is the same as that of nMOS operation in weak inversion mode, indicates that the PTnMOS operation in weak inversion mode is turned off. Figure 9 shows the carrier concentration under the gate oxide of PTnMOS at different gate bias voltages. The change in carrier concentration along B to B' can be observed. When the PTnMOS is operating in the ON-state (VG = − 1 V), a large number of holes are attracted under the gate oxide. Conversely, in the OFF-state (VG = 1 V), a large number of electrons are attracted under the gate oxide of the PTnMOS. This phenomenon is identical to that of nMOS. Because the PTnMOS operation is ON-state during the accumulation mode, we are able to form a single-carrier CMOS with only electronic transmission with two nMOS device.

4.3 Optimized electrical characteristics of PTnMOS

Figure 10 illustrates the ID–VG characteristics of the PTnMOS in detail, showing that the punch-through current increases with the carrier concentration. It can be observed that the punch-through current of the PTnMOS is directly proportional to the concentration, and the punch-thourgh current increases by one order for each order of the carrier concentration; however, the ability to turn off the punch-through effect is reduced when the channel concentration reaches 1018 cm−3 and the source/drain concentration reaches 2 × 1018 cm−3, which deteriorates the electrical properties of the PTnMOS. From the conduction band diagram in Fig. 11, it can also be seen that as the concentration increases at VG = − 1 V, the potential barrier between the source and the channel decreases, making it easier for electrons to pass through the barrier. Additionally, higher concentrations allow more electrons to cross the barrier, resulting in an increase in punch-through current.

Figure 12 shows the effect of varying the semiconductor layer thickness on the ID–VG characteristics of the PTnMOS. The sub-threshold swing performance improves as the semiconductor layer thickness decreases. At a semiconductor layer thickness of 10 nm, the sub-threshold swing reaches 81 mV/dec with an Ion/Ioff ratio of 2.89 × 107, as shown in Fig. 13. Reducing the thickness of the semiconductor layer enhances the coverage of the depletion region between the gate oxide layer and the semiconductor layer. The depletion region between the source/channel and the drain/channel can be easily pushed away, preventing the punch-through current from continuing to flow, thus enabling the PTnMOS to achieve better sub-threshold swing and Ion/Ioff ratios. When the semiconductor layer is too thick, it becomes difficult to effectively push away the depletion region between the source/channel and the drain/channel. This leads to difficulty in interrupting the punch-through current, requiring a larger gate bias to increase the depletion region between the gate oxide layer and the semiconductor layer, which in turn interrupts the punch-through current. Consequently, the sub-threshold swing becomes worse and the Ion/Ioff ratio of PTnMOS decreases when body thickness becomes thicker.

4.4 Impact of drain induced barrier lowering-like (DIBL-like) on PTnMOS

Figure 14 shows the ID–VG characteristics of the PTnMOS at VD = 0.3 V (saturation region) and VD = 0.03 V (linear region). It can be seen that the PTnMOS utilizes the punch-through effect to enhance the electron injection by lowering the potential barrier between the source and the channel in the accumulation mode. In addition, as the punch-through effect increases (i.e., the drain bias increases), the more the potential barrier decreases and the punch-through current increases. This behaviour is similar to that of DIBL, but PTnMOS operates based on punch-through current rather than the channel carrier drift current of nMOS. Therefore, we refer to this as DIBL-like. This behavior results in a very large DIBL-like value, calculated to be 1185 mV/V. This value indicates that the output current of the PTnMOS is very sensitive to the voltage between the source and drain, and it also means that the charge time of a PTnMOS with pMOS characteristics is very short when charging, which is advantageous for controlling the charge time of the logic circuit. Figure 15 shows the relationship between VD = 0.3 V and VD = 0.03 V potential and lateral position. It can clearly see that the potential barriers between the source and the channel are significantly reduced. This therefore emphasizes the importance of the punch-through effect in the operation of punch-through nMOSFET and how it affects the relationship between gate voltage and drain current.

4.5 PTnMOS and nMOS form a single-carrier CMOS

We used Silvaco MixedMode to analyse the single-carrier CMOS and compare it with conventional CMOS (Wp/Wn = 1) and conventional CMOS (Wp/Wn = 3). The parameters of nMOS and pMOS are the same as those of PTnMOS. The DC performance of the three inverter circuits is measured by inserting a load capacitance (CL), which is the sum of the internal capacitances of the PTnMOS and nMOS for single-carrier CMOS, and the nMOS and pMOS for conventional CMOS. Figure 16 shows the voltage transfer curves of three circuits at different supply voltages. Since the sub-threshold characteristics of the PTnMOS can replace the pMOS in the conventional CMOS circuit, when the PTnMOS is the driver and the nMOS is the load, the single-carrier CMOS circuit can maintain good characteristics under different supply voltages (VDD). Figure 17 shows the voltage gain of three circuits at different supply voltages. The effect of the pMOS width adjustment is to achieve a ratio of pMOS to nMOS drive current of 1, which results in a slight increase in the voltage gain of conventional CMOS (Wp/Wn = 3) compared to that of single-carrier CMOS. The voltage gains at VDD = 0.5 V are 12.58 for single-carrier CMOS, 11.19 for conventional CMOS (Wp/Wn = 1), and 14.99 for conventional CMOS (Wp/Wn = 3), respectively. Figure 18 shows the butterfly curve of the three circuits at VDD = 0.5 V. The following mathematical equations can be used to calculate high noise margin (NMH) and low noise margin (NML) [25],

the input voltages VIL and VIH are the voltages with voltage gain dVout/dVin = − 1 in Fig. 18. VOL and VOH can also be calculated from the transfer characteristics by considering the minimum and maximum voltage values. Calculated from Eqs. (1) and (2), NMH and NML are 0.199 V and 0.183 V for single carrier CMOS. For conventional CMOS (Wp/Wn = 1) they are 0.214 V and 0.174 V. For conventional CMOS (Wp/Wn = 3) they are 0.197 V and 0.194 V. The percentages of VDD for single-carrier CMOS are 39% and 36%, while for conventional CMOS (Wp/Wn = 1) they are 42% and 34%, and for conventional CMOS (Wp/Wn = 3) they are 39% and 38%. It can be found that single-carrier CMOS exhibits symmetric noise margin compared to conventional CMOS (Wp/Wn = 1). Figure 19 shows the Iout–Vin characteristics of the three circuits at VDD = 0.5 V. The static power dissipation (PD) was calculated to be 2.76 nW for single-carrier CMOS, 2.16 nW for conventional CMOS (Wp/Wn = 1), and 3.76 nW for conventional CMOS (Wp/Wn = 1). It can be observed that the static power dissipation of single-carrier CMOS is lower than that of conventional CMOS (Wp/Wn = 3). Figure 20 shows the propagation time of the three circuits at low and high frequencies. In Fig. 20a the delay time at low frequency is calculated to be 1.52us for single carrier CMOS, 3us for conventional CMOS (Wp/Wn = 1) and 1.93us for conventional CMOS (Wp/Wn = 3). The results show that the delay time of single-carrier CMOS is 49% faster than conventional CMOS (Wp/Wn = 1) and is 21% faster than conventional CMOS (Wp/Wn = 3). And the high frequency delay time calculated in Fig. 20b is 29 ps for single carrier CMOS, 41 ps for conventional CMOS (Wp/Wn = 1), and 45 ps for conventional CMOS (Wp/Wn = 3). The results indicate that the delay time of single-carrier CMOS is 29% faster than that of conventional CMOS (Wp/Wn = 1) and 35% faster than conventional CMOS (Wp/Wn = 3). Figure 21 shows the DC performance comparison of three circuits. The results indicate that single-carrier CMOS exhibits superior DC performance compared to conventional CMOS (Wp/Wn = 1). This is due to the fact that the ratio of drive current between PTnMOS and nMOS is about 0.84 times, which is higher than the ratio of drive current between pMOS and nMOS, and the optimised PTnMOS has better electrical properties than the conventional pMOS.

5 Conclusion

We have proposed the use of PTnMOS to replace pMOS in conventional CMOS circuits. The operation mechanism and modes of PTnMOS have been explored to optimize their electrical performance. Additionally, the effect of DIBL-like on PTnMOS has been discussed. We realized single-carrier CMOS circuits without sizing and with only electron transmission. The single-carrier CMOS exhibits symmetrical noise margin and 29% faster delay time than conventional CMOS (Wp/Wn = 1). If single-carrier CMOS circuits are transformed into III–V group materials, II–VI group materials, or even two-dimensional materials, sizing becomes unnecessary, thereby resolving the issue of occupied area. The electrical performance of single-carrier CMOS circuits is greatly enhanced by the advantage of ultra-high electron mobility of these materials, making them suitable for modern low-voltage, low-power and high-speed switching CMOS circuits.

Data availability

The data and analyses generated in this study have been agreed to by all authors and are available from the corresponding authors upon reasonable request.

References

Wanlass F, Sah C. Nanowatt logic using field-effect metal-oxide semiconductor triodes. In: 1963 IEEE international solid-state circuits conference. Digest of technical papers, Philadelphia, PA, USA; 1963. pp. 32–33. https://doi.org/10.1109/ISSCC.1963.1157450.

Taur Y, et al. CMOS scaling into the nanometer regime. Proc IEEE. 1997;85(4):486–504. https://doi.org/10.1109/5.573737.

Kinugawa M, Kakumu M, Matsunaga J. Submicron 3D surface-orientation-optimized CMOS technology. In: 1986 symposium on VLSI Technology. Digest of technical papers, San Diego, CA, USA; 1986. pp. 17–18.

Goebel B, Schumann D, Bertagnolli E. Vertical N-channel MOSFETs for extremely high density memories: the impact of interface orientation on device performance. IEEE Trans Electron Devices. 2001;48(5):897–906. https://doi.org/10.1109/16.918237.

Kinugawa M, Kakumu M, Usami T, Matsunaga J. Effects of silicon surface orientation on submicron CMOS devices. In: 1985 International electron devices meeting, Washington, DC, USA; 1985. pp. 581–584. https://doi.org/10.1109/IEDM.1985.191038.

Ohmi T, Matsumoto K, Nakamura K, Makihara K, Takano J, Yamamoto K. Influence of silicon wafer surface orientation on very thin oxide quality. J Appl Phys. 1995;77(3):1159–64. https://doi.org/10.1063/1.358980.

Toriumi A, et al. Opportunities and challenges for Ge CMOS—control of interfacing field on Ge is a key (Invited Paper). Microelectron Eng. 2009;86(7):1571–6. https://doi.org/10.1016/j.mee.2009.03.052.

Zimmerman P, et al. High performance Ge pMOS devices using a Si-compatible process flow. In: 2006 International electron devices meeting, San Francisco, CA, USA; 2006. pp. 1–4. https://doi.org/10.1109/IEDM.2006.346870.

Hyun Lee C, Nishimura T, Tabata T, Zhao D, Nagashio K, Toriumi A. Characterization of electron mobility in ultrathin body germanium-on-insulator metal-insulator-semiconductor field-effect transistors. Appl Phys Lett. 2013;102(23):232107. https://doi.org/10.1063/1.4810002.

Yu X, Kang J, Takenaka M, Takagi S. Experimental study on carrier transport properties in extremely-thin body Ge-on-insulator (GOI) p-MOSFETs with GOI thickness down to 2 nm. In: 2015 IEEE international electron devices meeting (IEDM), Washington, DC, USA; 2015. pp. 2.2.1–2.2.4. https://doi.org/10.1109/IEDM.2015.7409611.

Flachowsky S, et al. Understanding strain-induced drive-current enhancement in strained-silicon n-MOSFET and p-MOSFET. IEEE Trans Electron Devices. 2010;57(6):1343–54. https://doi.org/10.1109/TED.2010.2046461.

Yang HS, et al. Dual stress liner for high performance sub-45nm gate length SOI CMOS manufacturing. In: IEDM technical digest. IEEE international electron devices meeting, 2004., San Francisco, CA, USA; 2004. pp. 1075–1077. https://doi.org/10.1109/IEDM.2004.1419385.

Ghani T, et al. A 90 nm high volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors. In: IEEE international electron devices meeting 2003, Washington, DC, USA; 2003. pp. 11.6.1–11.6.3. https://doi.org/10.1109/IEDM.2003.1269442.

Chen CH, et al. Stress memorization technique (SMT) by selectively strained-nitride cap** for sub-65nm high-performance strained-Si device application. In: Digest of technical papers. 2004 Symposium on VLSI Technology, 2004, Honolulu, HI, USA; 2004. pp. 56–57. https://doi.org/10.1109/VLSIT.2004.1345390.

Auth C. 45 nm high-k + metal gate strain-enhanced CMOS transistors. In: 2008 IEEE custom integrated circuits conference, San Jose, CA, USA; 2008. pp. 379–386.https://doi.org/10.1109/CICC.2008.4672101.

Lin JT, Haga S, Shih MT, Lin YH. A new low power unipolar CMOS. In: 2014 12th IEEE international conference on solid-state and integrated circuit technology (ICSICT), Guilin, China; 2014. pp. 1–4.https://doi.org/10.1109/ICSICT.2014.7021282.

Lin CH, Lin JT, Chen HH, Eng YC, Wang SW. Unipolar CMOS inverter based on punch-through effect with two embedded oxide structure. In: 2011 IEEE international conference of electron devices and solid-state circuits, Tian**, China; 2011. pp. 1–2. https://doi.org/10.1109/EDSSC.2011.6117607.

Shin C, et al. Performance and area scaling benefits of FD-SOI technology for 6-T SRAM cells at the 22-nm node. IEEE Trans Electron Devices. 2010;57(6):1301–9. https://doi.org/10.1109/TED.2010.2046070.

Suryagandh SS, Garg M, Woo JCS. A device design methodology for sub-100-nm SOC applications using bulk and SOI MOSFETs. IEEE Trans Electron Devices. 2004;51(7):1122–8. https://doi.org/10.1109/TED.2004.829872.

Kilchytska V, et al. Influence of device engineering on the analog and RF performances of SOI MOSFETs. IEEE Trans Electron Devices. 2003;50(3):577–88. https://doi.org/10.1109/TED.2003.810471.

Hsu FC, Muller RS, Hu C, Ko PK. A simple punchthrough model for short-channel MOSFET’s. IEEE Trans Electron Devices. 1983;30(10):1354–9. https://doi.org/10.1109/T-ED.1983.21298.

Carter R, et al. 22 nm FDSOI technology for emerging mobile, Internet-of-Things, and RF applications. In: 2016 IEEE international electron devices meeting (IEDM), San Francisco, CA, USA; 2016. pp. 2.2.1–2.2.4. https://doi.org/10.1109/IEDM.2016.7838029.

ATHENA User’s Manual. Device simulation software. Santa Clara: Silvaco International Inc.; 2023.

ATLAS User’s Manual. Device simulation software. Santa Clara: Silvaco International Inc.; 2023.

Sreenivasulu VB, Narendar V. Design insights of nanosheet FET and CMOS circuit applications at 5-nm technology node. IEEE Trans Electron Devices. 2022;69(8):4115–22. https://doi.org/10.1109/TED.2022.3181575.

Acknowledgements

This work was supported in part by the Ministry of Science and Technology of Taiwan, R.O.C., under Contact MOST109-2221-E-110-018-MY3.

Author information

Authors and Affiliations

Contributions

Jyi-Tsong Lin: Provide initial concepts, guide, and revise the content of the manuscript. Pei-Zhang **e: Conduct simulation experiments and research, prepared all figures, and wrote manuscript content. Wei-Han Lee: Provide research proposals and review the content of the manuscript. Three authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lin, JT., **e, PZ. & Lee, WH. Enhancement noise margin and delay time performance of novel punch-through nMOS for single-carrier CMOS. Discover Nano 19, 113 (2024). https://doi.org/10.1186/s11671-024-04064-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/s11671-024-04064-y