Abstract

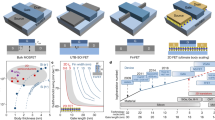

The primary challenge facing silicon-based electronics, crucial for modern technological progress, is difficulty in dimensional scaling. This stems from a severe deterioration of transistor performance due to carrier scattering when silicon thickness is reduced below a few nanometres. Atomically thin two-dimensional (2D) semiconductors still maintain their electrical characteristics even at sub-nanometre scales and offer the potential for monolithic three-dimensional (3D) integration. Here we explore a strategic shift aimed at addressing the scaling bottleneck of silicon by adopting 2D semiconductors as new channel materials. Examining both academic and industrial viewpoints, we delve into the latest trends in channel materials, the integration of metal contacts and gate dielectrics, and offer insights into the emerging landscape of industrializing 2D semiconductor-based transistors for monolithic 3D integration.

Similar content being viewed by others

References

Moore, G. E. Cramming more components onto integrated circuits. Proc. IEEE 86, 82–85 (1998).

Moore, G. E. Progress in digital integrated electronics. In Technical Digest. International Electron Devices Meeting (IEDM) 11–13 (IEEE, 1975). This article discusses the complexity of integrated circuits, identifies their manufacture, production and deployment and addresses trends to their future deployment.

Hu, C. Future CMOS scaling and reliability. Proc. IEEE 81, 682–689 (1993).

Packan, P. A. Pushing the limits. Science 285, 2079–2081 (1999).

Pop, E., Sinha, S. & Goodson, K. E. Heat generation and transport in nanometer-scale transistors. Proc. IEEE 94, 1587–1601 (2006).

Yan, R.-H., Ourmazd, A. & Lee, K. F. Scaling the Si MOSFET: from bulk to SOI to bulk. IEEE Trans. Electron Devices 39, 1704–1710 (1992).

Hisamoto, D. et al. FinFET—a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 47, 2320–2325 (2000).

Singh, N. et al. High-performance fully depleted silicon nanowire (diameter ≤ 5 nm) gate-all-around CMOS devices. IEEE Electron Device Lett. 27, 383–386 (2006).

Ryckaert, J., et al. Enabling sub-5 nm CMOS technology scaling thinner and taller! 2019 IEEE International Electron Devices Meeting (IEDM) 29.4.1–29.4.4 (IEEE, 2019).

The International Technology Roadmap for Semiconductors (ITRS) 2005 Edition (SIA, 2005); https://www.semiconductors.org

Reggiani, S. et al. Low-field electron mobility model for ultrathin-body SOI and double-gate MOSFETs with extremely small silicon thicknesses. IEEE Trans. Electron Devices 54, 2204–2212 (2007).

International Roadmap for Devices and Systems (IRDS) 2022 Edition (IEEE, 2022); https://irds.ieee.org/editions/2022

Lee, H.-H. S. & Chakrabarty, K. Test challenges for 3D integrated circuits. IEEE Des. Test. Comput. 26, 26–35 (2009).

Garrou, P., Bower, C. & Ramm, P. (eds) Handbook of 3D Integration, Volume 1: Technology and Applications of 3D Integrated Circuits (Wiley, 2011).

Liu, C., et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020). This is an examination of the performance improvement and device innovation that are inspired by 2D materials.

Liu, H., Neal, A. T. & Ye, P. D. Channel length scaling of MoS2 MOSFETs. ACS Nano 6, 8563–8569 (2012).

Shim, J. et al. Controlled crack propagation for atomic precision handling of wafer-scale two-dimensional materials. Science 362, 665–670 (2018). This article reports that monolayers of a variety of 2D materials can be cleaved from multilayers grown as 5-cm-diameter wafers.

Yu, H. et al. Wafer-scale growth and transfer of highly-oriented monolayer MoS2 continuous films. ACS Nano 11, 12001–12007 (2017).

Lin, Y.-C. et al. Wafer-scale MoS2 thin layers prepared by MoO3 sulfurization. Nanoscale 4, 6637–6641 (2012).

Kong, W. et al. Path towards graphene commercialization from lab to market. Nat. Nanotechnol. 14, 927–938 (2019). This article looks back at the past decade and gives an overview of the development history of graphene, commercial opportunities and the recent progress of graphene commercialization.

Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. Nature 520, 656–660 (2015). This article reports the preparation of high-mobility monolayer MoS2 and WS2 grown on 4 in. wafers with excellent spatial homogeneity over the entire films.

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021). This article demonstrates the epitaxial growth of monolayer MoS2 single crystals on a C-plane sapphire.

Liu, L. et al. Uniform nucleation and epitaxy of bilayer molybdenum disulfide on sapphire. Nature 605, 69–75 (2022).

Li, J. et al. General synthesis of two-dimensional van der Waals heterostructure arrays. Nature 579, 368–374 (2020).

Zhang, Z. et al. Endoepitaxial growth of monolayer mosaic heterostructures. Nat. Nanotechnol. 17, 493–499 (2022).

Kim, K. S. et al. Non-epitaxial single-crystal 2D material growth by geometric confinement. Nature 614, 88–94 (2023). This article reports a non-epitaxial strategy to grow single-domain TMDs on amorphous oxides, thus enabling direct growth of single-crystalline 2D materials on an Si wafer coated with an oxide layer.

**ong, X., et al. Demonstration of vertically-stacked CVD monolayer channels: MoS2 nanosheets GAA-FET with Ion > 700 µA/µm and MoS2/WSe2 CFET. In 2021 IEEE International Electron Devices Meeting (IEDM) 7.5.1–7.5.4 (IEEE, 2021).

O’Brien, K. P. et al. Process integration and future outlook of 2D transistors. Nat. Commun. 14, 6400 (2023).

Chung, Y.-Y. et al. First demonstration of GAA monolayer–MoS2 nanosheet nFET with 410 μA μm ID 1 V VD at 40 nm gate length. 2022 International Electron Devices Meeting (IEDM) 34–35 (IEEE, 2022).

Loi, F. et al. Growth mechanism and thermal stability of a MoS2–graphene interface: a high-resolution core-level photoelectron spectroscopy study. J. Phys. Chem. C 124, 20889–20897 (2020).

Pandey, A. et al. Structural and optical properties of bulk MoS2 for 2D layer growth. Adv. Mater. Lett. 7, 777–782 (2016).

Jiang, Y. et al. Physical adsorption and oxidation of ultrathin MoS2 crystals: insights into surface engineering for 2D electronics and beyond. Nanotechnology 34, 405701 (2023).

Jiang, J. et al. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023).

Boby, S. M. & Islam, R. MoS2 based TFET: study on channel thickness dependent performance. In 2018 4th International Conference on Electrical Engineering and Information & Communication Technology (iCEEiCT) 449–453 (IEEE, 2018).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

Wang, Y. et al. P-type electrical contacts for 2D transition-metal dichalcogenides. Nature 610, 61–66 (2022).

Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 557, 696–700 (2018).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Wang, L. et al. One-dimensional electrical contact to a two-dimensional material. Science 342, 614–617 (2013).

Moon, B. H. et al. Junction-structure-dependent Schottky barrier inhomogeneity and device ideality of monolayer MoS2 field-effect transistors. ACS Appl. Mater. Interfaces 9, 11240–11246 (2017).

Song, S. et al. Atomic transistors based on seamless lateral metal–semiconductor junctions with a sub-1-nm transfer length. Nat. Commun. 13, 4916 (2022).

Kim, H. G. & Lee, H.-B.-R. Atomic layer deposition on 2D materials. Chem. Mater. 29, 3809–3826 (2017).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

English, C. D. et al. Improved contacts to MoS2 transistors by ultra-high vacuum metal deposition. Nano Lett. 16, 3824–3830 (2016).

Gao, L. et al. Silicon-processes-compatible contact engineering for two-dimensional materials integrated circuits. Nano Res. 16, 12471–12490 (2023).

Chou, A.-S. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. In 2021 IEEE International Electron Devices Meeting (IEDM) 7.2.1–7.2.4 (IEEE, 2021).

Gu, M. et al. Hybrid low‐k spacer scheme for advanced FinFET technology parasitic capacitance reduction. Electron. Lett. 56, 514–516 (2020).

Lee, D. et al. Recessed-channel WSe2 field-effect transistor via self-terminated do** and layer-by-layer etching. ACS Nano 16, 8484–8492 (2022).

Kato, R. et al. p-type conversion of WS2 and WSe2 by position-selective oxidation do** and its application in top gate transistors. ACS Appl. Mater. Interfaces 15, 26977–26984 (2023).

Bolshakov, P. et al. Contact engineering for dual-gate MoS2 transistors using O2 plasma exposure. ACS Appl. Electron. Mater. 1, 210–219 (2019).

Zhao, P. et al. Probing interface defects in top-gated MoS2 transistors with impedance spectroscopy. ACS Appl. Mater. Interfaces 9, 24348–24356 (2017).

Yang, W. et al. The integration of sub-10 nm gate oxide on MoS2 with ultra low leakage and enhanced mobility. Sci. Rep. 5, 11921 (2015).

Zou, X. et al. Interface engineering for high‐performance top‐gated MoS2 field‐effect transistors. Adv. Mater. 26, 6255–6261 (2014).

Kim, H. et al. Ultrathin monolithic HfO2 formed by Hf-seeded atomic layer deposition on MoS2: film characteristics and its transistor application. Thin Solid Films 673, 112–118 (2019).

Dorow, C. et al. Advancing monolayer 2-D nMOS and pMOS transistor integration from growth to van der Waals interface engineering for ultimate CMOS scaling. IEEE Trans. Electron Devices 68, 6592–6598 (2021).

Wang, X., Scott, M. T. & Dai, H. Atomic layer deposition of metal oxides on pristine and functionalized graphene. J. Am. Chem. Soc. 130, 8152–8153 (2008).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Xu, Y. et al. Scalable integration of hybrid high-κ dielectric materials on two-dimensional semiconductors. Nat. Mater. 22, 1078–1084 (2023).

Park, Y. H. et al. Enhanced nucleation of high-k dielectrics on graphene by atomic layer deposition. Chem. Mater. 28, 7268–7275 (2016).

Fisichella, G. et al. Interface electrical properties of Al2O3 thin films on graphene obtained by atomic layer deposition with an in situ seedlike layer. ACS Appl. Mater. Interfaces 9, 7761–7771 (2017).

Lin, Y.-S. et al. Atomic layer deposition of sub-10 nm high-K gate dielectrics on top-gated MoS2 transistors without surface functionalization. Appl. Surf. Sci. 443, 421–428 (2018).

Lin, D., et al. Dual gate synthetic WS2 MOSFETs with 120 μS/μm Gm 2.7 μF/cm2 capacitance and ambipolar channel. In 2020 IEEE International Electron Devices Meeting (IEDM) 3.6.1–3.6.4 (IEEE, 2020).

Wu, X., et al. Dual gate synthetic MoS2 MOSFETs with 4.56 µF/cm2 channel capacitance, 320 µS/µm Gm and 420 µA/µm Id at 1 V Vd/100 nm Lg. In 2021 IEEE International Electron Devices Meeting (IEDM) 7.4.1–7.4.4 (IEEE, 2021).

Liu, K. et al. A wafer-scale van der Waals dielectric made from an inorganic molecular crystal film. Nat. Electron. 4, 906–913 (2021).

Lai, S. et al. HfO2/HfS2 hybrid heterostructure fabricated via controllable chemical conversion of two-dimensional HfS2. Nanoscale 10, 18758–18766 (2018).

Zhang, Y. et al. A single-crystalline native dielectric for two-dimensional semiconductors with an equivalent oxide thickness below 0.5 nm. Nat. Electron. 5, 643–649 (2022).

Yang, A. J. et al. Van der Waals integration of high-κ perovskite oxides and two-dimensional semiconductors. Nat. Electron. 5, 233–240 (2022).

Lu, Z. et al. Wafer-scale high-κ dielectrics for two-dimensional circuits via van der Waals integration. Nat. Commun. 14, 2340 (2023).

Britnell, L. et al. Electron tunneling through ultrathin boron nitride crystalline barriers. Nano Lett. 12, 1707–1710 (2012).

Knobloch, T. et al. The performance limits of hexagonal boron nitride as an insulator for scaled CMOS devices based on two-dimensional materials. Nat. Electron. 4, 98–108 (2021).

Fleetwood, D. M. et al. Effects of oxide traps, interface traps, and ‘border traps’ on metal–oxide–semiconductor devices. J. Appl. Phys. 73, 5058–5074 (1993).

Zhao, P. et al. Evaluation of border traps and interface traps in HfO2/MoS2 gate stacks by capacitance–voltage analysis. 2D Mater. 5, 031002 (2018).

Illarionov, Y. Y. et al. Energetic map** of oxide traps in MoS2 field-effect transistors. 2D Mater. 4, 025108 (2017).

Knobloch, T. et al. Improving stability in two-dimensional transistors with amorphous gate oxides by Fermi-level tuning. Nat. Electron. 5, 356–366 (2022).

O’Brien, K. P., et al. Advancing 2D monolayer CMOS through contact, channel and interface engineering. In 2021 IEEE International Electron Devices Meeting (IEDM) 7.1.1–7.1.4 (IEEE, 2021).

Smets, Q., et al. Scaling of double-gated WS2 FETs to sub-5 nm physical gate length fabricated in a 300 mm FAB. In 2021 IEEE International Electron Devices Meeting (IEDM) 34.2.1–34.2.4 (IEEE, 2021).

Schram, T., et al. High yield and process uniformity for 300 mm integrated WS2 FETs. In 2021 Symposium on VLSI Technology 1–2 (IEEE, 2021).

Hung, T. Y. T., et al. Pinning-free edge contact monolayer MoS2 FET. In 2020 IEEE International Electron Devices Meeting (IEDM) 3.3.1–3.3.4 (IEEE, 2020).

Nguyen, V. L. et al. Wafer-scale integration of transition metal dichalcogenide field-effect transistors using adhesion lithography. Nat. Electron. 6, 146–153 (2023).

Sohn, A. et al. Precise layer control and electronic state modulation of a transition metal dichalcogenide via phase‐transition‐induced growth. Adv. Mater. 34, 2103286 (2022).

Seol, M. et al. High‐throughput growth of wafer‐scale monolayer transition metal dichalcogenide via vertical Ostwald ripening. Adv. Mater. 32, 2003542 (2020). This article reports high-throughput growth of wafer-scale monolayer MoS2 and WS2.

Jang, H. et al. An atomically thin optoelectronic machine vision processor. Adv. Mater. 32, 2002431 (2020).

Gao, C. et al. Defect evolution behaviors from single sulfur point vacancies to line vacancies in monolayer molybdenum disulfide. Phys. Chem. Chem. Phys. 23, 19525–19536 (2021).

Mignuzzi, S. et al. Effect of disorder on Raman scattering of single-layer MoS2. Phys. Rev. B 91, 195411 (2015).

Chow, P. K. et al. Defect-induced photoluminescence in monolayer semiconducting transition metal dichalcogenides. ACS Nano 9, 1520–1527 (2015).

Ermolaev, G. A. et al. Broadband optical properties of monolayer and bulk MoS2. npj 2D Mater. Appl. 4, 21 (2020).

Syari’ati, A. et al. Photoemission spectroscopy study of structural defects in molybdenum disulfide (MoS2) grown by chemical vapor deposition (CVD). Chem. Commun. 55, 10384–10387 (2019).

Ma, N. & Jena, D. Charge scattering and mobility in atomically thin semiconductors. Phys. Rev. 4, 011043 (2014).

Yalon, E. et al. Energy dissipation in monolayer MoS2 electronics. Nano Lett. 17, 3429–3433 (2017).

Noel, J.-P. et al. Multi-VT UTBB FDSOI device architectures for low-power CMOS circuit. IEEE Trans. Electron Devices 58, 2473–2482 (2011).

Yoon, J.-S. et al. Multi-Vth strategies of 7-nm node nanosheet FETs with limited nanosheet spacing. IEEE J. Electron Devices Soc. 6, 861–865 (2018).

Schwierz, F. & Liou, J. J. Status and future prospects of CMOS scaling and Moore’s law—a personal perspective. In 2020 IEEE Latin America Electron Devices Conference (LAEDC) 1–4 (IEEE, 2020).

Radisavljevic, B. et al. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011). This article reports a realization of a field-effect transistor with a single, two-dimensional layer of the semiconductor MoS2.

Zhan, Y. et al. Large‐area vapor‐phase growth and characterization of MoS2 atomic layers on a SiO2 substrate. Small 8, 966–971 (2012).

Han, G. H. et al. Seeded growth of highly crystalline molybdenum disulphide monolayers at controlled locations. Nat. Commun. 6, 6128 (2015).

Wang, P. et al. Arrayed van der Waals broadband detectors for dual‐band detection. Adv. Mater. 29, 1604439 (2017).

Li, Y. et al. Site-specific positioning and patterning of MoS2 monolayers: the role of Au seeding. ACS Nano 12, 8970–8976 (2018).

Zhu, J. et al. Low-thermal-budget synthesis of monolayer molybdenum disulfide for silicon back-end-of-line integration on a 200 mm platform. Nat. Nanotechnol. 18, 456–463 (2023).

Fang, H. et al. High-performance single layered WSe2 p-FETs with chemically doped contacts. Nano Lett. 12, 3788–3792 (2012).

Kappera, R. et al. Phase-engineered low-resistance contacts for ultrathin MoS2 transistors. Nat. Mater. 13, 1128–1134 (2014).

Azcatl, A. et al. MoS2 functionalization for ultrathin atomic layer deposited dielectrics. Appl. Phys. Lett. 104, 111601 (2014).

Cheng, L. et al. Atomic layer deposition of a high-k dielectric on MoS2 using trimethylaluminum and ozone. ACS Appl. Mater. Interfaces 6, 11834–11838 (2014).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

Chen, M.-C., et al. TMD FinFET with 4 nm thin body and back gate control for future low power technology. In 2015 IEEE International Electron Devices Meeting (IEDM) 32.2.1–32.2.4 (IEEE, 2015).

Wachter, S. et al. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017).

Huang, X., et al. High drive and low leakage current MBC FET with channel thickness 1.2 nm/0.6 nm. 2020 IEEE International Electron Devices Meeting (IEDM) 12.1.1–12.1.4 (IEEE, 2020).

**ong, X., et al. Top-gate CVD WSe2 pFETs with record-high Id ~ 594 μA/μm, Gm ~ 244 μS/μm and WSe2/MoS2 CFET based half-adder circuit using monolithic 3D integration. In 2022 International Electron Devices Meeting (IEDM) 20–26 (IEEE, 2022).

Choi, M. S. et al. Recent progress in 1D contacts for 2D‐material‐based devices. Adv. Mater. 34, 2202408 (2022).

Smithe, K. K. H., Suryavanshi, S. V., Munoz Rojo, M., Tedjarati, A. D. & Pop, E. Low variability in synthetic monolayer MoS2 devices. ACS Nano 11, 8456–8463 (2017).

Chou, A. S. et al. High on-state current in chemical vapor deposited monolayer MoS2 nFETs with Sn ohmic contacts. IEEE Electron Device Lett. 42, 272–275 (2021).

Yang, L. et al. Chloride molecular do** technique on 2D materials: WS2 and MoS2. Nano Lett. 14, 6275–6280 (2014).

McClellan, J. et al. High current density in monolayer MoS2 doped by AlOx. ACS Nano 15, 1587–1596 (2021).

Cheng, Z. et al. Immunity to contact scaling in MoS2 transistors using in situ edge contacts. Nano Lett. 19, 5077–5085 (2019).

**ao, J. et al. Record-high saturation current in end-bond contacted monolayer MoS2 transistors. Nano Res. 15, 475–481 (2022).

Guimaraes, M. H. D. et al. Atomically thin ohmic edge contacts between two-dimensional materials. ACS Nano 10, 6392–6399 (2016).

Acknowledgements

This material is based on work supported by AFOSR (award no. FA9550-22-1-0024) and DARPA (award no. D19AP00037-07).

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Nanotechnology thanks Peng Zhou, Zheng Zhang and **ang Chen for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kim, K.S., Kwon, J., Ryu, H. et al. The future of two-dimensional semiconductors beyond Moore’s law. Nat. Nanotechnol. (2024). https://doi.org/10.1038/s41565-024-01695-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41565-024-01695-1

- Springer Nature Limited