Abstract

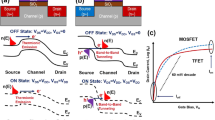

In the last few years, an accelerated trend towards the miniaturization of nanoscale circuits has been recorded. In this context, the Tunneling Field-Effect Transistors (TFETs) are gaining attention because of their good subthreshold characteristics, high scalability and low leakage current. However, they suffer from low values of the ON-state current and severe ambipolar transport mechanism. The aim of this work is to investigate the performance of SiGe nanoscale Double Gate TFET device including low doped drain region. The electrical performance of the considered device is investigated numerically using ATLAS 2D simulator, where both scaling and reliability aspects of the proposed design are reported. In this context, we address the impact of the channel length, traps density and drain do** parameters on the variation of some figures of merit of the device namely the swing factor and the ION/IOFF ratio. The obtained results indicate the superior immunity of the proposed design against traps induced degradation in comparison to the conventional TFET structure. Therefore, this work can offer more insights regarding the benefit of adopting channel materials and drain do** engineering techniques for future reliable low-power nanoscale electronic applications.

Similar content being viewed by others

References

Hu C (1991) Future CMOS scaling and reliability. Proc IEEE 81(05):682–689

Skotnicki T, Hutchby JA, King TJ, Wong HSP, Boeuf F (2005) The end of CMOS scaling: toward the introduction of new materials and structural changes to improve MOSFET performance. IEEE Circuits Devices Mag 21(01):16–26

Hemmat M, Kamal M, Afzali-Kusha A, Pedram M (2017) Hybrid TFET-MOSFET circuit: a solution to design soft-error resilient ultra-low power digital circuit. Integration 57:11–19

Ghoggali Z, Djeffal F (2010) Analytical analysis of nanoscale fully depleted double-gate MOSFETs including the hot-carrier degradation effects. Int J Electron 97(2):119–127

Mamaluy D, Gao X (2015) The fundamental downscaling limit of field effect transistors. Appl Phys Lett 106:193503–193503.5

Djeffal F, Ferhati H, Bentrcia T (2016) Improved analog and RF performances of gate-all-around junctionless MOSFET with drain and source extensions. Superlattice Microst 90:132–140

Djeffal F, Lakhdar N (2013) An improved analog electrical performance of submicron dual-material gate (DM) GaAs-MESFETs using multi-objective computation. J Comput Electron 12(01):29–35

Tamersit K, Djeffal F (2016) Double-gate Graphene Nanoribbon field-effect transistor for DNA and gas sensing applications: simulation study and sensitivity analysis. IEEE Sensors J 16(11):4180–4191

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479:329–337

Seabaugh AC, Zhang Q (2010) Low-voltage tunnel transistors for beyond CMOS logic. Proc IEEE 98(12):2095–2110

Esseni D, Guglielmini M, Kapidani B, Rollo T, Alioto M (2014) Tunnel FETs for ultralow voltage digital VLSI circuits: part I—device–circuit interaction and evaluation at device level. IEEE Trans Very Large Scale Integr VLSI Syst 22(12):2488–2498

Ferhati H, Djeffal F, Bentrcia T (2018) The role of the Ge mole fraction in improving the performance of a nanoscale junctionless tunneling FET: concept and scaling capability. Beilstein J Nanotechnol 09:1856–1862

Mamidala JK, Vishnoi R, Pandey P (2017) Tunnel field-effect transistors (TFET): Modelling and simulation. John Wiley, West Sussex

Le Royer C (2011) Interfaces and performance: what future for nanoscale Ge and SiGe based CMOS? Microelectron Eng 88(07):1541–1548

Mahajan R, Gautam DK (2016) Analysis of a SiGe MOSFET at 22nm. Silicon 08(04):505–511

Wu J, Taur Y (2016) Reduction of TFET OFF-current and subthreshold swing by lightly doped drain. IEEE Trans Electron Devices 63(08):3342–3345

Atlas User's Manual (2012) SILVACO TCAD

Seo JH, Yoon YJ, Lee S, Lee JH, Cho S, Kang IM (2015) Design and analysis of Si-based arch-shaped gate-all-around (GAA). Curr Appl Phys 15(03):208–212

Li ZYC, Guo J, Zhuang Y (2019) A GaAs0.5Sb0.5/In0.53Ga0.47As heterojunction Z-gate TFET with hetero-gate-dielectric. Superlattice Microst 129(05):282–293

Kardam U, Narang R, Saxena M, Gupta M (2019) Exploring the applicability of well optimized dielectric pocket tunnel transistor for future low power applications. Superlattice Microst 126(02):8–16

Tam S, Ko PK, Hu C (1984) Lucky-electron model of channel hot-electron injection in MOSFET'S. IEEE Trans Electron Devices 31(09):1116–1125

Abdi MA, Djeffal F, Dibi Z, Arar D (2011) A two-dimensional analytical subthreshold behavior analysis including hot-carrier effect for nanoscale gate stack gate all around (GASGAA) MOSFETs. J Comput Electron 10(1–2):179–185

Bentrcia T, Djeffal F, Benhaya A (2012) Continuous analytic I—V model for GS DG MOSFETs including hot-carrier degradation effects. J Semicond 33(01):014001(1–014001(6

Garg S, Saurabh S (2018) Suppression of ambipolar current in tunnel FETs using drain-pocket: proposal and analysis. Superlattice Microst 113(01):261–270

Boucart K (2010) “Simulation of double-gate silicon tunnel FETs with a high-k gate dielectric”. PhD Dissertation, École Polytechnique Fédérale de Lausanne, Switzerland

Chebaki E, Djeffal F, Ferhati H, Bentrcia T (2016) Improved analog/RF performance of double gate junctionless MOSFET using both gate material engineering and drain/source extensions. Superlattice Microst 92:80–91

Bentrcia T, Djeffal F, Chahdi M (2013) An analytical two dimensional subthreshold behavior model to study the nanoscale GCGS DG Si MOSFET including interfacial trap effects. Microelectron Reliab 53(04):520–527

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Bentrcia, T., Djeffal, F., Ferhati, H. et al. A Comparative Study on Scaling Capabilities of Si and SiGe Nanoscale Double Gate Tunneling FETs. Silicon 12, 945–953 (2020). https://doi.org/10.1007/s12633-019-00190-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-00190-w