Abstract

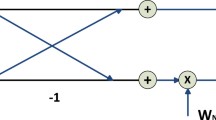

A highly configurable fast Fourier transform intellectual property core (FFT IP core) that can be mounted on Avalon bus of Nios II processor is designed in this paper, by the means of custom-built components in SOPC Builder. Not only the data number can be configured to 2n and the data width can be configured as integer or floating-point number of 32 bits, but also the number of inner butterfly units is configurable, which can effectively resolve the contradiction between speed and hardware resource occupancy. The IP core is designed by butterfly computing elements of a mixed radix-4 and radix-2 algorithm and applies the in-place addressing scheme and reusing method to reduce hardware resources consumption. Functional simulation by Quartus II platform proves that the results calculated by FFT IP core are accordant with the Matlab results. Hardware test on DE2 development board by timestamp timer demonstrates that the FFT IP core costs only 34.8 μs to achieve FFT of 512 sampled data with precision of 32-bit floating point. It is demonstrated that the IP core has the advantages of feasible configuration, easy use, and high precision.

Similar content being viewed by others

References

Choi J R, Park S B, Han D S, et al. A 2048 complex point FFT architecture for digital audio broadcasting system [C]// Proc IEEE Int Symp Circuits Syst. New York: IEEE Press, 2000: 693–696.

Yang **g, Zheng Enrang, Zhang Ling, et al. Design and realization of FFT processor based on FPGA [J]. Control and Instruments in Chemical Industry, 2010, (3): 107–109(Ch).

Lo H F, Shieh M D, Wu C M. Design of an efficient FFT processor for DAB system [C]// Proc IEEE Int Symp Circuits Systems (ISCAS). New York: IEEE Press, 2001: 654–657.

Veithen D, Spruyt P, Pollet T, et al. A 70 Mb/s variable-rate DMT-based modem for VDSL [C]// Proc Int Solid-State Circuits Conf. New York: IEEE Press, 1999: 248–249.

Radhouance R, Liu P, Modlin C. Minimizing the memory requirement for continuous flow FFT implementation: continuous flow mixed mode FFT (CFMM-FFT) [C]// Proc IEEE Int Symp Circuits Systems (ISCAS). New York: IEEE Press, 2000: 116–119.

He S, Torkelson M. Design and implementation of a 1024 point pipeline FFT processor [C]// Proc IEEE Custom Integrated Circuits. New York: IEEE Press, 1998: 131–134.

Jo B G, Sunwoo M H. New continuous flow mixed radix (CFMR) FFT processor using novel in-place strategy [J]. Proc IEEE Trans Circuit and Systems, 2005, 52(5): 911–919.

Amphion. CS2410 8-1024 point FFT/IFFT [EB/OL]. [2011-10-12]. http://www.amphion.com .

Drey Enterprise Inc. Jaguar II variable-point (8-1024) FFT-IFFT specification [EB/OL]. [2011-10-25]. http://www.dreyenterpriseinc.com .

Altera Corporation. Nios II processor reference handbook, version 10.1 [EB/OL]. [2011-09-17]. http://www.altera.com.cn/literature .

Altera Corporation. Quartus II handbook version 10.2. Volume 4: SOPC Builder [EB/OL]. [2011-10-10]. http://www.altera.com.cn/literature .

Jiang Liangwei, Long Fengli, Cheng Jian. Design of user IP component in SOPC builder [J]. Nuclear Electronics and Detection Technology, 2009, (29): 172–176(Ch).

Altera Corporation. FFT Mega core function user guide, version 10.2[EB/OL]. [2011-11-23]. http://www.altera.com.cn/literature .

Nadehara K, Miyazaki T, Kuroda I. Radix-4 FFT implementation using SIMD multimedia instructions [C]// Proc IEEE Int Conf Acoust, Speech, Signal Processing (ICASSP). New York: IEEE Press, 1999: 2131–2134.

Choi J R, Park S B, Han D S, et al. A 2048 complex point FFT architecture for digital audio broadcasting system [C]// Proc IEEE Int Symp Circuits Syst. New York: IEEE Press, 2000: 693–696.

Author information

Authors and Affiliations

Corresponding author

Additional information

Foundation item: Supported by the Natural Science Foundation of Hubei Province (2011CDC017)

Biography: LIU Sanjun, male, Ph.D. candidate, research direction: information theory, multiuser communications, embedded system and SOPC technology.

Rights and permissions

About this article

Cite this article

Liu, S., Sun, L., Li, S. et al. Highly configurable floating-point FFT IP Core with reusing method. Wuhan Univ. J. Nat. Sci. 18, 59–66 (2013). https://doi.org/10.1007/s11859-013-0894-z

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11859-013-0894-z