Abstract

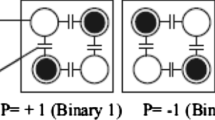

Processing-in-memory (PIM) is a computing paradigm through which computations and processing can be performed within the memory of a computer, server, or related devices. There are several ways to implement PIM architectures, but the combination of Akers array and quantum-dot cellular automata (QCA) helps to achieve high-speed computing at the nanoscale. In this research, a novel PIM architecture is designed using Akers array based on binary QCA (BQCA) and ternary QCA (TQCA). Ternary systems are more efficient in performing logic operations, so they can positively affect the performance of PIM. To evaluate the performance of the proposed BQCA PIM cell, NAND and NOR gates are used. The evaluation results indicate the superiority of the proposed BQCA and TQCA PIM architectures over conventional computing paradigms in terms of area occupation and complexity.

Similar content being viewed by others

References

Jiang H, Peng X, Huang S et al (2020) CIMAT: a compute-in-memory architecture for on-chip training based on transpose SRAM arrays. IEEE Trans Comput. 69(7):944–954. https://doi.org/10.1109/TC.2020.2980533

**ngqi Z , Sheng X et al (2021) Breaking the von Neumann bottleneck: architecture-level processing-in-memory technology. Sci China Inf Sci. 64(6)

Gupta S, Imani M, Kaur H, Rosing TS (2019) NNPIM: a processing in-memory architecture for neural network acceleration. IEEE Trans Comput 68(9):1325–1337

Kang H, Gibbons P B, Blelloch G E (2021) The Processing-in-Memory Model. In: Proceedings of the 33rd ACM Symposium on Parallelism in Algorithms and Architectures, pp 295–306. https://doi.org/10.1145/3409964.3461816

Sudarshan C, Soliman T et al (2021) A Novel DRAM-Based Process-in-Memory Architecture and its Implementation for CNNs. ASPDAC '21 In: Proceedings of the 26th Asia and South Pacific Design Automation Conference, pp. 35–42. https://doi.org/10.1145/3394885.3431522

Akers B (1972) A rectangular logic array. IEEE Trans 8:848–857

Chougule PP, Sen B (2017) Dongale T D (2017) Realization of processing In-memory computing architecture using quantum dot cellular automata. Microprocess Microsyst 52:49–58

Safaiezadeh B, Mahdipour E, Haghparast M et al (2021) Novel design and simulation of reversible ALU in quantum dot cellular automata. J Supercomput. https://doi.org/10.1007/s11227-021-03860-y

Patidar M, Gupta N (2021) Efficient design and implementation of a robust coplanar crossover and multilayer hybrid full adder–subtractor using QCA technology. J Supercomput 77:7893–7915

Goswami M, Pal J, Choudhury MR, Chougule PP (2020) Sen B (2020) In memory computation using quantum-dot cellular automata. IET Comput Digital Tech 14(6):336–343

Hosseini SA, Roosta E (2021) A novel technique to produce logic ‘1’ in Multi-threshold ternary circuits design. Circuits Syst Signal Process 40:1152–1165. https://doi.org/10.1007/s00034-020-01535-2

Mohaghegh SM, Sabbaghi-Nadooshan R, Mohammadi M (2018) Innovative model for ternary QCA gates. IET Circuits Devices Syst 12(2):189–195

Akbari-Hasanjani R, Sabbaghi-Nadooshan R (2021) New design of binary to ternary converter. IETE J Res. https://doi.org/10.1080/03772063.2021.1886881

Navidia A, Sabbaghi-Nadooshan R, Dousti M TQCAsim: An Accurate Design and Essential Simulation Tool for Ternary Logic Quantum-Dot Cellular Automata. Scientia Iranica, 10:53471.3256

Chougule PP, Sen B, Mukherjee R, Patil PS, Kamat RK, Dongale TD (2017) A processing in memory realization using quantum dot cellular automata (QCA): proposal and implementation. J Nano-Electron Phys. https://doi.org/10.21272/jnep.9(1).01021

Bajec LI, Zimic N, Mraz M (2006) The ternary quantum-dot cell and ternary logic. Nanotechnology 17(8):1937–1942

Pecar P, Janez M, Zimic N et al (2009) The ternary quantum-dot cellular automata memorizing cell. In: Proceedings of Computer Society Annual Symp. on VLSI, Tampa, Florida, USA, pp 223–228

Pecar P, Ramsak A, Zimic N et al (2008) Adiabatic pipelining: a key to ternary computing with quantum dots. Nanotechnol. 19(49):495401

M Janez, L I Bajec, P Pecar, et al (2008) Automatic design of optimal logic circuits based on ternary quantum-dot cellular automata, World Scientific and Engineering Academy and Society (WSEAS 7(9):919–928

Levy Y, Bruck J, Cassuto Y, Friedman EG, Kolodny A, Yaakobi E, Kvatinsky S (2014) Logic operations in memory using a memristive Akers array. Microelectron 45:1429–1437

Jeon JC (2021) Designing nanotechnology QCA–multiplexer using majority function-based NAND for quantum computing. J Supercomput 77:1562–1578

Subramanyam D V S, Manideep D, Kumar V (2019) Study and Implementation of RAM Cell using a Novel 5 Input Majority Gate in QCA. International Journal of Research in Engineering, Science and Management 2(3):2581–5792

Mohammadi MN, Sabbaghi-Nadooshan R (2016) Introducing a novel model based on particle wave duality for energy dissipation analysis in MQCA circuits. J Comput Electron 15(2):683–896

Amlani I, Orlov AO, Kummamuru RK et al (2000) Experimental demonstration of a leadless quantum-dot cellular automata cell. Appl Phys 77(5):738–740

Cowburn R P (2003) Digital nanomagnetic logic. In: Proceedings of 61st Device Research Conference. Conference Digest Salt, Lake City, UT, USA, pp. 111–114

Pulecio J F, Bhanja S (2007) Reliability of bi-stable single domain nano magnets for cellular automata. In: Proceedings of IEEE Conf. Nanotechnology, Hong Kong, China, 2007, pp. 782–786

Das K, De D (2013) Realization of semiconductor ternary quantum dot cellular automata. IET Micro Nano 8(5):258–263

Kamali S F, Tabrizchi S et al (2020) Designing positive, negative and standard gates for ternary logics using quantum dot cellular automata. Comput Electric Eng. 83

Akbari- hasanjani R, Sabbaghi-Nadooshan R, Tanhayi M (2021) New polarization and power calculation with error elimination in Ternary QCA and simulation with new TQCA Sim. Accepted in Computer and Electrical Engineering

Asfestani MN, Heikalabad SR (2017) A unique structure for the multiplexer in quantum-dot cellular automata to create a revolution in design of nanostructures. Physica B: Phys Condensed Matter 512:91–99

Majeed AH, Alkaldy E, Zainal MS et al (2019) Optimal design of RAM cell using novel 2:1 multiplexer in QCA technology. Comput Sci Circuit World. https://doi.org/10.1108/CW-06-2019-0062

Dehkordi MA et al (2011) Novel RAM cell designs based on inherent capabilities of quantum-dot cellular. Microelectron 5(42):701–708. https://doi.org/10.1016/j.mejo.2011.02.006

Angizi S et al (2015) Design and evaluation of new majority gate-based RAM cell in quantum-dot cellular automata. Microelectron 46:43–51

Oh T, Jeong H, Kang K, Park J et al (2017) Power-Gated 9T SRAM Cell for Low-Energy Operation. IEEE Transactions Scale Int (VLSI) Systems 25(3):1183–1187

Yang Y, Park J, Song S C, Wang J, Yeap G, Jung S (2014) Single-Ended 9T SRAM Cell for Near-Threshold Voltage Operation with Enhanced Read Performance in 22-nm FinFET Technology. IEEE Trans Very Large Scale Integrat (VLSI) Systems. 23(11): 2748–2752

Walus K et al (2003) RAM design using quantum-dot cellular automata. In: Proceedings of Conference record of the NanoTechnology, University of British Columbia–Vancouver. pp. 160-163

Hashemi S, Navi K (2012) New robust QCA D flip flop and memory structures. Microelectron 43(12):929–940

Rezaie Fam S, Navimipour N J (2019) Design of a loop-based random access memory based on the nanoscale quantum dot cellular automata. Photonic Network Communications 37(1)

Shin C, Damrongplasit N et al (2011) Performance and yield benefits of quasi-planar bulk CMOS technology for 6-T SRAM at the 22-nm node. IEEE Trans Electron Devices 58(7):1846–1854

Karl E, Guo Z, Conary J et al (2016) A 0.6 V, 1.5 GHz 84 Mb SRAM in 14 nm FinFET CMOS Technology with capacitive charge-sharing write assist circuitry. IEEE Journal of Solid-State Circuits 51(1):222–229

Bhoi B, Misra N, Pradhan M (2017) Design and evaluation of an efficient parity-preserving reversible QCA gate with online testability. Cogent Eng 4(1):1416888. https://doi.org/10.1080/23311916.2017.1416888

Zahoor F et al (2020) CNT and RRAM based unbalanced ternary logic gates and basic arithmetic circuits. IEEE Access 8

Doostaregan A, Abrishamifar A (2020) On the design of robust, low power with high noise immunity quaternary circuits. Microelectron J. 102:104774

Abdullah-Al-Shafi M, Ziaur R (2019) Analysis and modeling of sequential circuits in QCA nano computing: RAM and SISO register study. Solid State Electronics Letters 1:73–83

Abdullah-Al-Shafi M, Bahar AN (2019) A new structure for random access memory using quantum-dot cellular automata. Sens 17(8):595–600

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Dehbozorgi, L., Sabbaghi-Nadooshan, R. & Kashaninia, A. Realization of processing-in-memory using binary and ternary quantum-dot cellular automata. J Supercomput 78, 6846–6874 (2022). https://doi.org/10.1007/s11227-021-04152-1

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-021-04152-1