Abstract

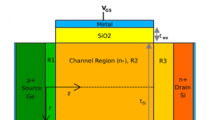

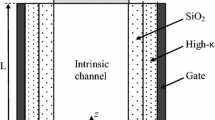

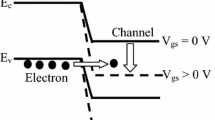

A semianalytical model based on a nonlocal approach is proposed for an undoped tunnel field-effect transistor (TFET) with a vertical surrounding-gate structure. The heterostructure band alignment is computed by applying the affinity rule on suitable potential expressions obtained from the two-dimensional (2-D) electrostatic solution for all device regions. The fringing field, do**-induced degeneracy, ambipolarity, and dual modulation effects are included with the aim of obtaining a large domain of validity. The core model is completed with expressions for the capacitance of the terminals and validated against numerical simulations obtained using ATLAS-2D software. An investigation of the types of band alignment and the impact of do** on the device performance is also conducted. The developed models could be implemented into commercial simulators to investigate circuits based on such multigate field-effect transistors (FETs).

Similar content being viewed by others

References

Mookerjea, S., et al: Experimental demonstration of 100 nm channel length In0.53Ga0.47As-based vertical inter-band tunnel field effect transistors (TFETs) for ultra low-power logic and SRAM applications. In: 2009 IEEE International Electron Devices Meeting (IEDM), pp. 1–3. IEEE (2009)

Dewey, G., et al.: Fabrication, characterization, and physics of III–V heterojunction tunneling field effect transistors (H-TFET) for steep sub-threshold swing. In: IEEE International Electron Devices Meeting (IEDM), Washington, DC, pp. 785–788. (2011)

Knoch, J., Appenzeller, J.: Modeling of high-performance p-type III–V heterojunction tunnel FETs. IEEE Electron Device Lett. 31, 305–307 (2010)

Verhulst, A.S., Vandenberghe, W.G., Maex, K., Groeseneken, G.: Boosting the on-current of a n-channel nanowire tunnel field-effect transistor by source material optimization. J. Appl. Phys. 104, 064514 (2008)

Convertino, C., Zota, C.B., Schmid, H., Ionescu, A.M., Moselund, K.E.: III–V heterostructure tunnel field-effect transistor. J. Phys. Condens. Matter 30, 264005 (2018)

De Michielis, L., et al.: Tunneling and occupancy probabilities: how do they affect tunnel-FET behavior? IEEE Electron Device Lett. 34, 726–728 (2013)

Dong, Y., et al.: A compact model for double-gate heterojunction tunnel FETs. IEEE Trans. Electron Devices 63, 4506–4513 (2016)

Jain, P., et al.: Band-to-band tunneling in Γ valley for Ge source lateral tunnel field effect transistor: thickness scaling. J. Appl. Phys. 122, 014502 (2017)

Guan, Y., et al.: An analytical model of gate-all-around heterojunction tunneling FET. IEEE Trans. Electron Devices 65, 776–782 (2018)

Penn State III–V Tunnel FET Model Manual. https://nanohub.org/

Taur, Y., Wu, J., Min, J.: An analytic model for heterojunction tunnel FETs with exponential barrier. IEEE Trans. Electron Devices 62, 1399–1404 (2015)

Min, J., Wu, J., Taur, Y.: Analysis of source do** effect in tunnel FETs with staggered bandgap. IEEE Electron Device Lett. 36, 1094–1096 (2015)

Abdelmalek, N., Djeffal, F., Bentrcia, T.: Continuous semianalytical modeling of vertical surrounding-gate tunnel FET: analog/RF performance evaluation. J. Comput. Electron. 17, 724–735 (2018)

ATLAS User Manual: Device Simulation Software (2012)

Anvarifard, M.K., Orouji, A.A.: Proper electrostatic modulation of electric field in a reliable nano-SOI with a developed channel. IEEE Trans. Electron Devices 65, 1653–1657 (2018)

Anvarifard, M.K., Orouji, A.A.: Stop** electric field extension in a modified nanostructure based on SOI technology-A comprehensive numerical study. Superlattices Microstruct. 111, 206–220 (2017)

Bardon, M.G., Neves, H.P., Puers, R., Hoof, C.V.: Pseudo-two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans. Electron Devices 57, 827–834 (2010)

Vishnoi, R., Kumar, M.J.: A pseudo-2-D-analytical model of dual material gate all-around nanowire tunneling FET. IEEE Trans. Electron Devices 61, 2264–2270 (2014)

Shen, C., et al.: A variational approach to the two-dimensional nonlinear Poisson’s equation for the modeling of tunneling transistors. IEEE Trans. Electron Devices 29, 1252–1255 (2008)

Jazaeri, F.: Modeling junctionless metal-oxide-semiconductor field-effect transistor. Ph.D. dissertation, École Polytechnique Fédérale de Lausanne (EPFL), Switzerland (2015)

Lin, S.C., Kuo, J.B.: Modeling the fringing electric field effect on the threshold voltage of FD SOI nMOS devices with the LDD/sidewall oxide spacer structure. IEEE Trans. Electron Devices 50, 2559–2564 (2003)

Bansal, A., Paul, B.C., Roy, K.: An analytical fringe capacitance model for interconnects using conformal map**. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 25, 2765–2774 (2006)

Plonsey, R., Collin, R.E.: Principles and Applications of Electromagnetic Fields. McGraw-Hill Book Company, New York (1961)

Anderson, R.L.: Experiments on Ge–GaAs heterojunction. Solid State Electron. 5, 341–344 (1962)

Kane, E.O.: Zener tunneling in semiconductors. J. Phys. Chem. Solids 12, 181–188 (1960)

Tanaka, S.: A unified theory of direct and indirect interband tunneling under a nonuniform electric field. Solid State Electron. 37, 1543–1552 (1994)

Milnes, A.G., Feuct, D.L.: Heterojunctions and Metal Semiconductor Junctions. Academic, New York (1972)

Koswatta, S.O., Koester, S.J., Haensch, W.: On the possibility of obtaining MOSFET-like performance and sub-60-mV/dec swing in 1-D broken-gap tunnel transistors. IEEE Trans. Electron Devices 57, 3222–3230 (2010)

Seabaugh, A.C., Zhang, Q.: Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98, 2095–2110 (2010)

Rajamohanan, B.: Fabrication, characterization and physics of III–V tunneling field effect transistors for low power logic and RF applications. Ph.D. dissertation, Pennsylvania State University (2010)

Lundstrom, M.S., Schuelke, R.J.: Modeling semiconductor heterojunctions in equilibrium. Solid State Electron. 25, 683–691 (1982)

Mookerjea, S., Krishnan, R., Datta, S., Narayanan, V.: On enhanced Miller capacitance effect in interband tunnel transistors. IEEE Electron Device Lett. 30, 1102–1104 (2009)

Zhang, L., Lin, X., He, J., Chan, M.: An analytical charge model for double-gate tunnel FETs. IEEE Trans. Electron Devices 59, 3217–3223 (2012)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Abdelmalek, N., Djeffal, F. & Bentrcia, T. A nonlocal approach for semianalytical modeling of a heterojunction vertical surrounding-gate tunnel FET. J Comput Electron 18, 104–119 (2019). https://doi.org/10.1007/s10825-019-01302-w

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-019-01302-w