Abstract

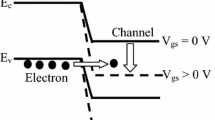

A continuous and accurate model based on the two-dimensional (2D) potential solution of a tunnel field-effect transistor (TFET) with undoped vertical surrounding-gate (VSG) structure is proposed. Both ambipolarity and dual modulation effects are included to obtain a more accurate analytical model, whose validity is demonstrated by comparison with two-dimensional numerical simulations using ATLAS-2D. The continuity of the proposed model enables extraction of analog/radiofrequency (RF) parameters and device figures of merit. Moreover, the effect of introducing a high-\(\kappa \) layer on the gate oxide in improving the behavior of the VSG-TFET is explored for use in high-performance analog/RF applications. The proposed continuous analytical model can be easily implemented in commercial simulators to study and investigate VSG-TFET-based nanoelectronic circuits.

Similar content being viewed by others

References

International Technology Roadmap for Semiconductors (ITRS). http://itrs.net (2013). Accessed 20 Dec 2013

Chen, Q., Meindl, J.D.: Nanoscale metal oxide semiconductor field effect transistors: scaling limits and opportunities. Nanotechnology 15, 8549–8555 (2004)

Bentrcia, T., Djeffal, F., Benhaya, A.: Continuous analytic I–V model for GS DG MOSFETs including hot-carrier degradation effects. J. Semicond. 33, 14001–14006 (2012)

Djeffal, F., Ferhati, H., Bentrcia, T.: Improved analog and RF performances of gate-all-around junctionless MOSFET with drain and source extensions. Superlattices Microstruct. 90, 132–140 (2016)

ITRS Summer Meeting, Palo Alto, CA, July 11–12 (2015)

Luong, G.V., et al.: Complementary strained Si GAA nanowire TFET inverter with suppressed ambipolarity. IEEE Electron Device Lett. 37, 950–953 (2016)

Schulte-Braucks, C., et al.: Experimental demonstration of improved analog device performance of nanowire-TFETs. Solid State Electron. 113, 179–183 (2015)

Datta, S., Liu, H., Narayanan, V.: Tunnel FET technology: a reliability perspective. In: Microelectronics Reliability, vol. 54, pp. 861–874 (2014)

Seabaugh, A.C., Zhang, Q.: Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98, 2095–2110 (2010)

Schmitt-Landsiedel, D., Werner, C.: "Innovative devices for integrated circuits—a design perspective,"Solid-State. Electronics 53, 411–417 (2009)

Liu, L., Mohata, D., Datta, S.: Scaling length theory of double-gate interband tunnel field-effect transistors, IEEE Trans. Electron Devices 59, 902–908 (2012)

Chien, N.D., Shih, C.H.: Short channel effects in tunnel field-effect transistors with different configurations of abrupt and graded Si/SiGe heterojunctions. Superlattices Microstruct. 100, 857–866 (2016)

Biswal, S.M., Baral, B., De, D., Sarkar, A.: Study of effect of gate-length downscaling on the analog/RF performance and linearity investigation of InAs-based nanowire Tunnel FET. Superlattices Microstruct. 91, 319–330 (2016)

Lee, J.S., et al.: Simulation study on effect of drain underlap in gate-all-around tunneling field-effect transistors. Curr. Appl. Phys. 13, 1143–1149 (2013)

Kane, E.O.: Zener tunneling in semiconductors. J. Phys. Chem. Solids 12, 181–188 (1960)

Ahmed, K., Monzure Elahi, M.M., Shofiqul Islam, Md.: A compact analytical model of band-to-band tunneling in a nanoscale p-i-n diode. In: International Conference on Informatics, Electronics & Vision (ICIEV), Dhaka, Bangladesh, 18–19 May (2012)

Bhushan, B., Nayak, K., Rao, V.R.: DC compact model for SOI tunnel field-effect transistors. IEEE Trans. Electron Devices 59, 2635–2642 (2012)

Taur, Y., Wu, J., Min, J.: An analytic model for heterojunction tunnel FETs with exponential barrier. In: IEEE Transactions on Electron Devices, vol. 62, pp. 1399–1404 (2015)

Mamidala, J.K., Vishnoi, R., Pandey, P.: Tunnel field-effect transistors (TFET): modeling and simulation. Wiley, New York (2017)

Kane, E.O.: Theory of tunneling. J. Appl. Phys. 32, 83–91 (1961)

Bardon, M.G., Neves, H.P., Puers, R., Hoof, C.V.: Pseudo-two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans. Electron Devices 57, 827–834 (2010)

Zhang, L., Lin, X., He, J., Chan, M.: An analytical charge model for double-gate tunnel FETs. IEEE Trans Electron Devices 59, 3217–3223 (2012)

Shen, C., et al.: A variational approach to the two-dimensional nonlinear poisson’s equation for the modeling of tunneling transistors. IEEE Trans. Electron Devices 29, 1252–1255 (2008)

Pan, A., Chen, S., Chui, C.O.: Electrostatic modeling and insights regarding multigate lateral tunneling transistors. IEEE Trans. Electron Devices 60, 2712–2720 (2013)

Patel, P.A.: Steep turn on/off green tunnel transistors, PhD dissertation. University of California, Berkeley (2010)

Zhang, L., Chan, M.: SPICE modeling of double-gate tunnel-FETs including channel transports. IEEE Trans. Electron Devices 61, 300–307 (2014)

Pal, A., Dutta, A.K.: Analytical drain current modeling of double-gate tunnel field-effect transistors. IEEE Trans Electron Devices 63, 3213–3221 (2016)

Min, J., Wu, J., Taur, Y.: Analysis of source do** effect in tunnel FETs with staggered bandgap. IEEE Electron Device Lett. 36, 1094–1096 (2015)

Tajik Khaveh, H.R., Mohammadi, S.: Potential and drain current modeling of gate-all-around tunnel FETs considering the junctions depletion regions and the channel mobile charge carriers. IEEE Trans. Electron Devices 63, 5021–5029 (2016)

Gholizadeh, M., Hosseini, S.E.: A 2-D analytical model for double-gate tunnel FETs. In: IEEE Transactions on Electron Devices, vol. 61, pp. 1494–1500 (2014)

ATLAS User Manual: Device Simulation Software (2012)

Wu, C., Huang, R., Huang, Q.: An analytical surface potential model accounting for the dual-modulation effects in tunnel FETs, IEEE Trans. Electron Devices 61, 2690–2696 (2014)

Abd El Hamid, H., Iñíguez, B., Guitart, J.R.: Analytical model of the threshold voltage and subthreshold swing of undoped cylindrical gate-all-around-based MOSFETs. IEEE Trans Electron Devices 54, 572–579 (2007)

Chambré, P.L.: On the solution of the Poisson–Boltzmann equation with application to the theory of thermal explosions. J. Chem. Phys. 20, 1795–1797 (1952)

Polyanin, A.D.: Handbook of Linear Partial Differential Equation for Engineers and Scientists. Chapman & Hall/CRC, London (2002)

Asmar, N.H.: Partial Differential Equations with Fourier Series and Boundary Value Problems. Pearson Prentice Hall, Upper Saddle River (2004)

Ray, B., Mahapatra, S.: Modeling and analysis of body potential of cylindrical gate-all-around nanowire transistor. IEEE Trans. Electron Devices 55, 2409–2416 (2008)

Abdi, D.B., Kumar, M.J.: 2-D threshold voltage model for the double-gate p-n-p-n TFET with localized charges. IEEE Trans. Electron Devices 63, 3663–3668 (2016)

Rechem, D., Khial, A., Azizi, C., Djeffal, F.: Impacts of high-k gate dielectrics and low temperature on the performance of nanoscale CNTFETs. J. Comput. Electron. 15, 1308–1315 (2016)

Cornetta, G., Santos, D.J., Vazquez, J.M.: Wireless Radio-Frequency Standards and System Design: Advanced Techniques, 1st edn. IGI Publishing Hershey, Hershey (2012)

Baruah, R.K., Paily, R.P.: A dual material double-layer gate stack junctionless transistor for enhanced analog performance. In: VLSI Design and Test 17th International Symposium, VDAT 2013, Jaipur, India, July 27–30 (2013)

Razavi, B.: RF Microelectronics. Prentice Hall, Englewood (1998)

Ma, W., Kaya, S.: Impact of device physics on DG and SOI MOSFET linearity. Solid State Electron. 48, 1741–1746 (2004)

Bentrcia, T., Djeffal, F., Chebaki, E., Arar, D.: Impact of the drain and source extensions on nanoscale Double-Gate Junctionless MOSFET analog and RF performances. Mater. Sci. Semicond. Process. 42, 264–267 (2016)

Rogers, J., Plett, C.: Radio Freq. Integr. Circuit Des. Artech House, Norwood (2003)

Lee, T.H.: The Design of CMOS Radio-Frequency Integrated Circuits, 2nd edn. Cambridge University Press, Cambridge (2004)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Abdelmalek, N., Djeffal, F. & Bentrcia, T. Continuous semianalytical modeling of vertical surrounding-gate tunnel FET: analog/RF performance evaluation. J Comput Electron 17, 724–735 (2018). https://doi.org/10.1007/s10825-018-1141-9

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-018-1141-9